# Lecture Notes and Practical Courses on System on Chip (SoC): Materials for Embedded Systems Subjects

József VÁSÁRHELYI & Ahmed BOUZID

**First Edition**

Authors:Dr. habil. József VÁSÁRHELYI, Associate Professor<br/>Dr. Ahmed BOUZID, Adjunct ProfessorLecturer:Dr. Rabab BENOTSMANE, Assistant LecturerEditor:University of MiskolcKeywords:Embedded Systems, FPGA, SoC, Computational Technologies, HDL

November 2021

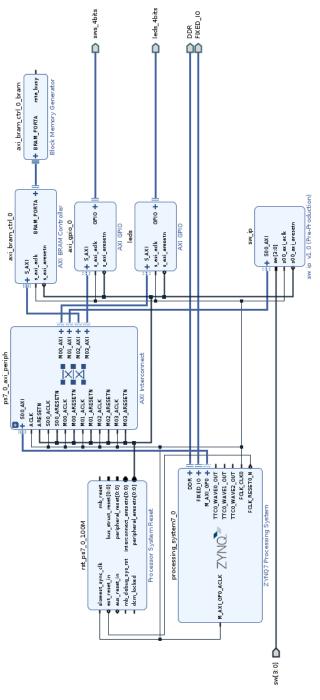

All rights reserved. No part of this book may be reproduced, in any form or by any means without permission in writing from the publisher.

ISBN 978-963-358-238-1

### M40A>> ATMK1 449H >>H>>>

Translation: There is no rose without thorns.

Hungarian proverb

QOET OXX:Q XOO EO SENNO :+D:XOGOO ONOXNEE X:O SECOI

Translation: Always aim for the moon; if you miss, you'll land among the stars.

Amazigh (Berber) proverb

i

# **Contents**

| 1 | Emb | edded System Architectures – System on Chip Anatomy            | 1  |  |  |  |  |  |

|---|-----|----------------------------------------------------------------|----|--|--|--|--|--|

|   | 1.1 | Introduction to Embedded Systems                               | 1  |  |  |  |  |  |

|   | 1.2 | System on Chip (SoC)                                           | 1  |  |  |  |  |  |

|   |     | 1.2.1 Introduction to SoCs                                     | 1  |  |  |  |  |  |

|   |     | 1.2.2 The Principle of SoCs                                    | 3  |  |  |  |  |  |

| 2 | The | ne Zyng device 9                                               |    |  |  |  |  |  |

|   | 2.1 | Introduction                                                   | 9  |  |  |  |  |  |

|   | 2.2 | Zynq-7000 Overview                                             | 10 |  |  |  |  |  |

|   | 2.3 | The Zyng Processing System                                     | 10 |  |  |  |  |  |

|   |     |                                                                | 10 |  |  |  |  |  |

|   |     | 2.3.2 Memory interfaces                                        | 16 |  |  |  |  |  |

|   |     | 2.3.3 Processing System Interconnect                           | 16 |  |  |  |  |  |

|   |     |                                                                | 16 |  |  |  |  |  |

|   |     | 2.3.5 PS Boots first                                           | 16 |  |  |  |  |  |

|   |     | 2.3.6 Clock resources                                          | 17 |  |  |  |  |  |

|   | 2.4 | Summary                                                        | 17 |  |  |  |  |  |

| 3 | VHD | VHDL hardware description language 19                          |    |  |  |  |  |  |

|   | 3.1 | Introduction to Hardware Description Language                  | 19 |  |  |  |  |  |

|   | 3.2 |                                                                | 20 |  |  |  |  |  |

|   | 3.3 |                                                                | 21 |  |  |  |  |  |

|   |     |                                                                | 22 |  |  |  |  |  |

|   |     | 3.3.2 Verilog hardware description language                    | 22 |  |  |  |  |  |

|   |     |                                                                | 23 |  |  |  |  |  |

|   | 3.4 |                                                                | 23 |  |  |  |  |  |

|   |     | 3.4.1 Entity as the interface model                            | 25 |  |  |  |  |  |

|   |     | 3.4.2 Architecture as model functionality, behavior, structure | 25 |  |  |  |  |  |

|   |     | 3.4.3 Constants and Signals                                    | 27 |  |  |  |  |  |

|   |     | 3.4.4 Packages, Libraries                                      | 27 |  |  |  |  |  |

|   |     | -                                                              | 28 |  |  |  |  |  |

|   |     | 3.4.6 VHDL Objects                                             | 28 |  |  |  |  |  |

|   |     | 3.4.7 Data types and operations                                | 29 |  |  |  |  |  |

BEFEKTETÉS A JÖVŐBE

ii

|   | 3.5  | Behavioral system description in VHDL                               | 30  |  |  |  |  |

|---|------|---------------------------------------------------------------------|-----|--|--|--|--|

|   |      | 3.5.1 Combinational Signal Assignments                              | 30  |  |  |  |  |

|   |      | 3.5.2 Sequential signal assignments                                 | 31  |  |  |  |  |

|   |      | 3.5.3 Conditional Decisions in processes                            | 34  |  |  |  |  |

|   | 3.6  | Structural description in VHDL                                      | 36  |  |  |  |  |

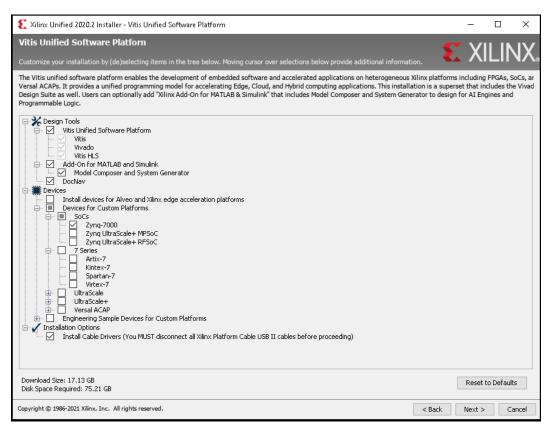

| 4 | Hard | Hardware and software setup                                         |     |  |  |  |  |

|   | 4.1  |                                                                     | 42  |  |  |  |  |

|   |      |                                                                     | 47  |  |  |  |  |

|   |      | 5                                                                   | 48  |  |  |  |  |

|   | 4.2  | 5                                                                   | 48  |  |  |  |  |

|   | 4.3  | UART-USB driver install                                             | 49  |  |  |  |  |

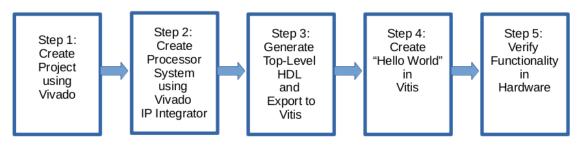

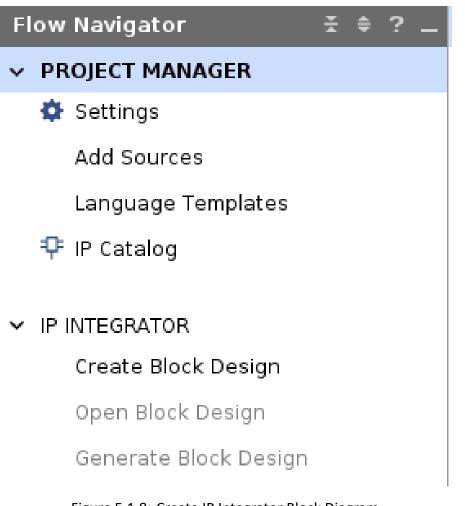

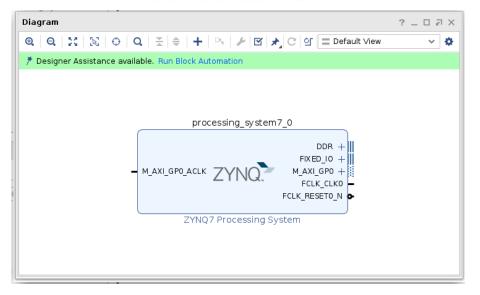

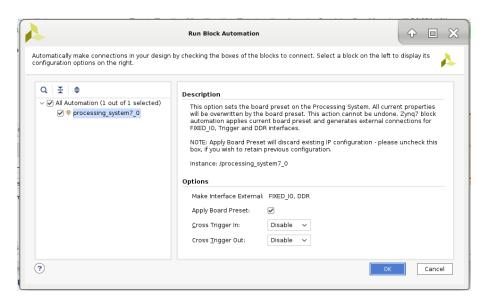

| 5 | Emb  | edded system Design with Zynq, hardware and software design basics  | 51  |  |  |  |  |

|   | 5.1  |                                                                     | 52  |  |  |  |  |

|   |      |                                                                     | 52  |  |  |  |  |

|   |      |                                                                     | 80  |  |  |  |  |

|   | 5.2  | $\cdots$                                                            | 99  |  |  |  |  |

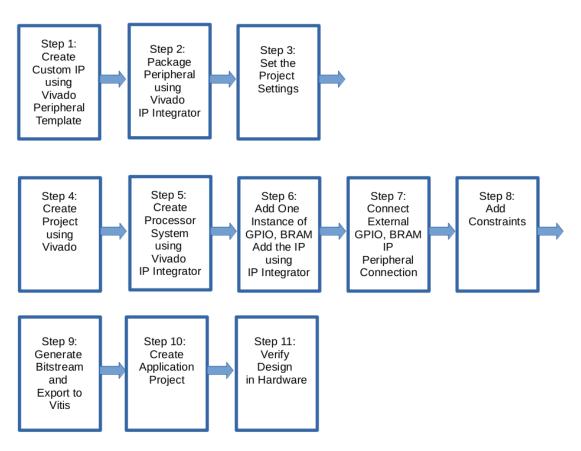

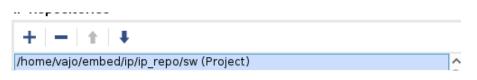

|   |      | 5.2.1 Create and Manage IP Project                                  |     |  |  |  |  |

|   |      | 5.2.2 Create the Vivado Project with User Designed IP               |     |  |  |  |  |

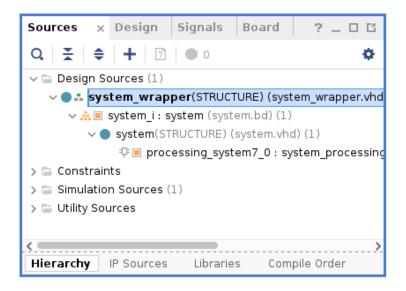

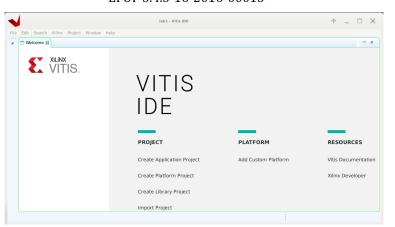

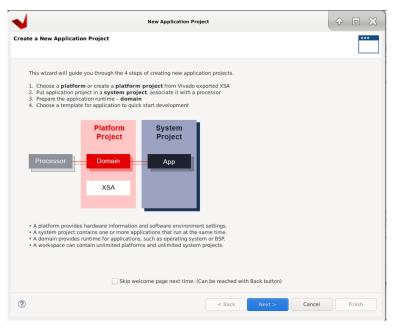

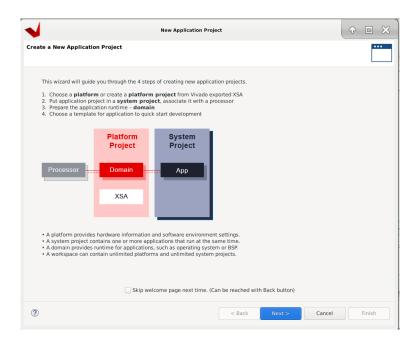

|   |      | 5.2.3 Launch Vitis and Generate the Test Application of the project | 131 |  |  |  |  |

| 6 |      |                                                                     | 142 |  |  |  |  |

|   | 6.1  |                                                                     |     |  |  |  |  |

|   |      |                                                                     | 143 |  |  |  |  |

|   |      | 6.1.1 Phase 1: Coding and Simulation                                |     |  |  |  |  |

|   |      | 6.1.2 Phase 2: Hardware design, Implementation and Test             |     |  |  |  |  |

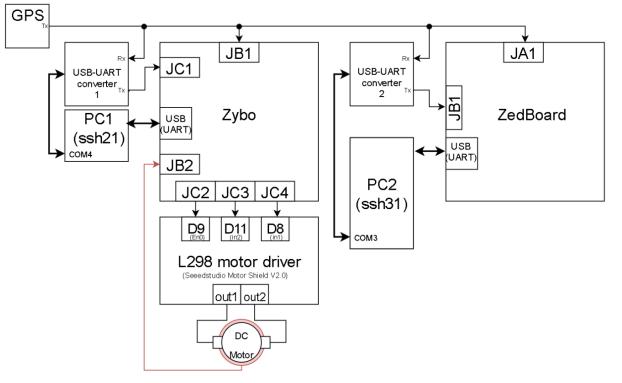

|   | 6.2  | Project 2: Remote DC Motor Control using SoC and Hall effect Sensor | 144 |  |  |  |  |

| 7 | Exer |                                                                     | L45 |  |  |  |  |

|   | 7.1  | Multiple Choice Quizzes                                             |     |  |  |  |  |

|   | 7.2  | Questions                                                           | 146 |  |  |  |  |

| Α | Addi |                                                                     | 151 |  |  |  |  |

|   | A.1  | GPS Data                                                            |     |  |  |  |  |

|   |      | A.1.1 10 seconds 1Hz GPS NMEA (correct data)                        |     |  |  |  |  |

|   |      | A.1.2 10 seconds 1Hz GPS NMEA (incorrect data)                      | 152 |  |  |  |  |

# Chapter 1

# Embedded System Architectures – System on Chip Anatomy

# **1.1 Introduction to Embedded Systems**

Is a computing system that has been designed to accomplish a single specific application. Embedded systems can be based on homogeneous and heterogeneous technologies. The most familiar ones are the digital, analog or mixed-signal integrated circuits. However, some other technologies are not excluded since they offer better performances for some applications, for instance Quantium computers, Integrated Fluidic Circuits, Photonic Integrated Circuits and many other Unconventional computing systems.

Microcontrollers and Microprocessor are basically not embedded systems before being programmed.

# 1.2 System on Chip (SoC)

## **1.2.1** Introduction to SoCs

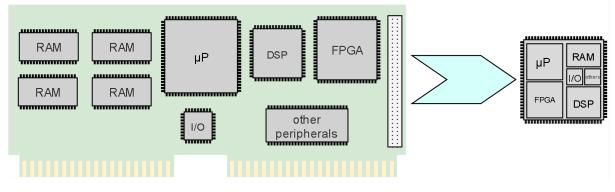

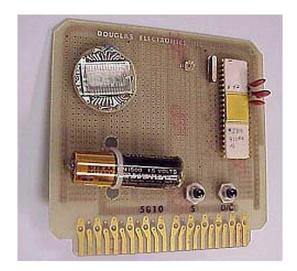

The advance of microelectronics allows the reduction of the size of transistors to get them embedded in increasingly small spaces. This ability to miniaturize components gives us the possibility of integrating different components in the same chip that were previously connected in a PCB (Printed Circuit Board) (See fig. 1.1). We are therefore witnessing the development of SoCs (System on Chip). Previously a digital computer was a single logic gate. Gathering those logic gates according to a specific architecture gives birth to processors. The packaging and miniaturization of these processors is the key point in the creation of microprocessors. What mainly differs between microprocessors and microcontrollers is the autonomy in terms of computation; in other words, microprocessors need other components, called peripherals (e.g. memory, I/O ...), for normal operation. That said, if in addition to peripherals

"FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

are added other computing units from other technologies (Graphical Processors, Sound Processors ...), gives a System-on-Chip.

Figure 1.1: Miniaturization from a Printed Circuit Board to a System on Chip

The interest is to minimize the size, the energy consumption and above all to expand the fields of application. SoCs are a systematic result of the miniaturisation of processors, in consequence, they are useful for creating custom architectures that can accelerate microcontrollers or microprocessors for some tasks.

A hardware accelerator is a computational element that helps the main processing system to perform some tasks. The latter can be: matrix computations, floating point operations, image processing, digital signal processing... In addition to some tasks that cannot be performed by a digital processor such us: conditioning and analog signal processing.

SoCs allow to create other architectures and take benefits of design reuse by means of the emergence of IPs (Intellectual Properties). This leads to the ease of reuse, the reduction of time to market and therefore cheaper products.

#### Moore's Law

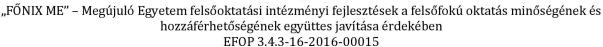

According to Gordon Moore, in 1965 the number of transistors in a given area on a chip could double every 18-24 months [Moo98]. In other words, it is possible to double the efficiency of semiconductor technology, and therefore chips, every two years or so while keeping the same power consumption. This law has enabled manufacturers of microelectronic manufacturing to clearly define their objectives and avoid unfair competition. 40 years after Moore's prediction, i.e. in 2005, the latter himself mentioned the future of this law which will end around 2025. Indeed, if we follow the evolution curve of the size of the transistors (Fig. 1.2), we can see that by 2025 the size will be around 2nm which is roughly equivalent to the size of two glucose molecules.

Figure 1.2: The evolution of the number of transistors, their density and size

## **1.2.2** The Principle of SoCs

A System-on-Chip (SoC) is a circuit that packages computing elements into a single die dedicated for an autonomous task. From this definition one could understand that previously the elements of calculations were separated in different chips. These computers can be simple transistors from their basic purposes/function (switch inverter, amplification), to more complex circuits (memories, processors...). Computers have more and more functionalities thanks to the ability to merge multiple heterogeneous technologies in the same chip such as mixed-signal integrated circuits.

An SoC can be defined by the integration of computational technologies into a single chip. From this definition SoC could divided into 3 types, these types are chronologically ordered:

**Specialized SoCs**, which also belongs to the family of ASICs (Application-Specific Integrated Circuit) since they are dedicated to a specific application.

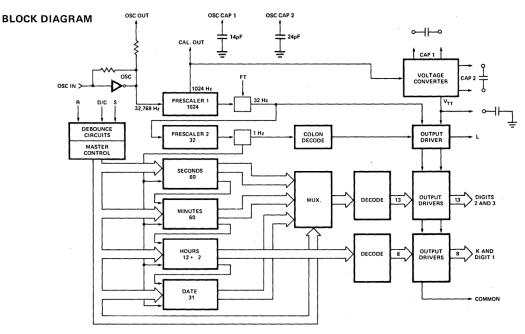

The first System-on-Chip was an Intel 5810A CMOS chip created in 1972 for Microma-Seiko digital watches. The IC has two functions: LCD driver and timer. [Cor76] [Jr.07]

The Microma liquid crystal display (LCD) digital watch is the first product to integrate a complete electronic system onto a single silicon chip. [CGL<sup>+</sup>20] [VSM01] [HKM08]

Figure 1.3: The first wristwatch equipped with a dedicated SoC: The Seiko Microma in 1974 [Pre14]

Figure 1.4: The prototype of the Intel 5810A based watch [VSM01]

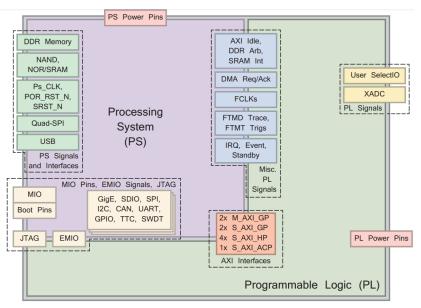

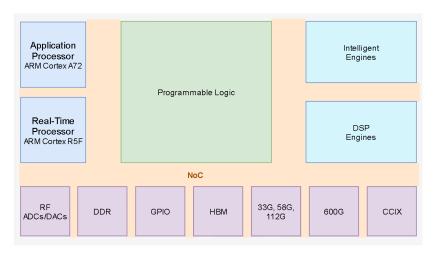

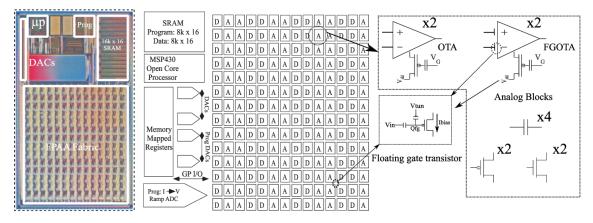

**Programmable SoCs.** This category concerns chips which contain a microprocessor, peripherals, and a programmable logic area (or FPGA). Zynq is a family of Xilinx SoCs which will be used to implement the labs proposed in this teaching material (see fig. 1.6). Actual research works propose chips where a programmable analog area is also included in the same chip which allows flexibility for mixed-signal (analog and digital) designs such as the RASP 3.0 (Reconfigurable Analog Signal Processor) (see 1.8). Actual Programmable SoCs (such as ACAP from Xilinx) are mainly a combination of microprocessors, FPGA, DSPs, GPU, RF, and notably Intelligent Engines capable of implementing artificial intelligent

Figure 1.5: Block diagram of the first SoC: the Intel 5810A [Cor76]

algorithms (See fig 1.7). Unlike Programmable SoCs, the previous category has the disadvantage of its fixed architecture and its impossibility to upgrade.

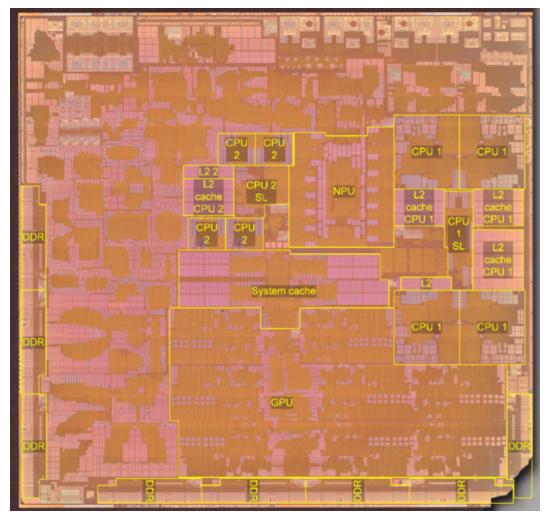

Figure 1.6: The architecture of Xilinx's Zynq Z-7010 SoC

Figure 1.7: The architecture of Xilinx's ACAP (Adaptive Compute Acceleration Platform)

"FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

Figure 1.8: The architecture of the RASP 3.0 (Reconfigurable Analog Signal Processor) [STGH19]

**Microprocessor based SoCs**. This type constitute the main concern of the actual market of mobile phones, tablets, and some laptops. In addition to a multicore microprocessor, these chips mainly contain a GPU, DSPs, memory, and peripherals. Comparing to Programmable SoCs, this type of SoCs are not reconfigurable i.e., its architecture is fixed, however contain much higher performance processors.

Figure 1.9: Detailed die photo of the Apple's M1 SoC (2020) [tec]

# **Chapter 2**

# The Zynq device

# 2.1 Introduction

In the previous chapter was mentioned the impact of Moore's law on the evolution of integrated circuits. There were treated the SOC structures in general and was mentioned that the first system on chip was created by Intel. We have to clarify that this Intel's SOC was not programmable by the user. In this sense this Intel 5810A was an Application Specific Integrated Circuit (ASIC). Before we introduce the Zynq device let us mention some milestones, which lead to the All Programmable System on Chip (AP-SOC) architecture, which is the Zynq device and also should be here mentioned the Adaptive Compute Acceleration Platform (ACAP), which is much more then a system on chip. First it should be mentioned Tsugio Makimoto's paper [Mak02] in which the author detailed that evolution of integrated circuit (IC) technology every ten years oscillating between the standardization and customization depending on the "technology crisis". Also the author predicted the second digital wave, which came after the PC world (representing the first digital wave). In this sense it was easy to predict that different user programmable circuits and fix function IC will converge in what we call today APSOC and ACAP. We can affirm that because of the "von Neumann centered" engineering world, since the appearance of the FPGA on the market, it became a challenge to implement in the FPGA a processor. VHDL (Very High Speed Integrated Circuit Hardware Description Language) offered the solution to integrate a so called soft processor in the FPGA. These processors (8051 and PIC) were not integrated physically in the chip but they were described in VHDL and embedded in the user design. One can realize that almost from beginning of the FPGA era appeared the need to have a processor together with the FPGA in the same chip.

The first *hard processor* physically integrated in a System on Chip (hard processor and FPGA) was the 8032 micro-controller realized by Triscend in 1998 and later this company integrated the ARM7 processor (Xilinx acquired Triscend in 2004). Since the department always used Xilinx FPGA and APSOC in research and education this chapter focus on the most current device used in the embedded systems, which is the Zynq device. The chapter will not give a detailed description of the device, since there is

a huge literature about the Zynq device [[ARMb], [CEES14], [Xil18b]] and other materials found on the Xilinx webpage.

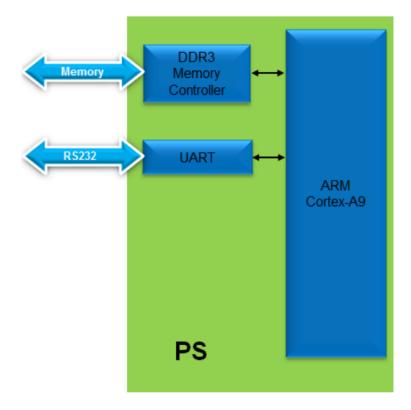

# 2.2 Zynq-7000 Overview

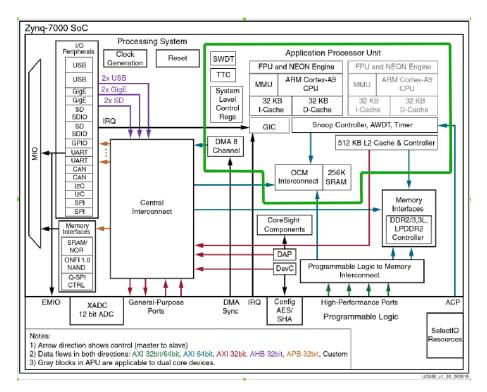

Based on the data sheet [Xil18b] The Zynq-7000 device is first generation architecture based on the Xilinx SoC architecture. The chip processing system (PS) integrate in the device a dual core ARM<sup>®</sup> Cortex<sup>™</sup>-A9 processor and programmable logic (PL) based on the 28 nm technology. Strictly speaking the Zynq device PS shows micro controller structure with its on-chip memory and external memory interfaces with a rich set of peripheral interfaces such as DMA controller, Ethernet MAC, USB 2.0B OTG interfaces, CAN 2.0B controllers, SD/SDIO 2.0/MMC3.31 compliant controllers, full duplex SPI ports, high-speed UARTs and multiplexed IOs for peripheral pin assignment. The connectivity within the PS and between the PS and PL it is realized with the AMBA<sup>®</sup> AXI standard interface bus. The programmable logic contains Configurable Logic Blocks (CLB), 36 Kb Block RAM, Digital Signal Processing (DSP) blocks, Programmable I/O Blocks (IOB), JTAG Boundary Scan interface, PCI Express<sup>®</sup> Block and two 12 bit Analog to Digital (AD) converters. With this reach architecture the Zynq-7000 device target "cost sensitive as well as high performance" embedded applications. In the following pages we will present the PS and the PL system. We underline that for an effective SoC embedded system development it is very important to have a deep knowledge about the hardware structure.

## 2.3 The Zynq Processing System

The hard processor integrated in all of Zynq devices is the ARM Cortex 9. The processing system incorporates not just the the ARM processor but also resources that come to extend the processor to a complex dual core micro controller. The Application Processing Unit (APU) is a dual core processing system. Each ARM processor has instruction and data cache, memory management unit (MMU) and a floating point NEON media processing engine for SIMD (Simple Instruction Multiple Data) support. The Accelerator coherency port (ACP) interface enable a coherent access from PL to CPU memory space. The 8-channel DMA supports multiple transfer types. Axi interface enable high throughput DMA transfers. Also the DMA has 4 channels to the PL. Interrupt are handled by the General Interrupt Controller (GIc), program execution can be controlled by the Watchdog Timers. The APU also has two triple timers/counters.

## 2.3.1 ARM processor

The ARM core have RISC architecture. RISC architectures have simple and powerful instructions, which are executed in a single clock cycle. Basically the RISC architecture reduces the complexity of instructions performed by the hardware and provide greater flexibility in software. For the ARM processors the RISC philosophy is implemented with four major considerations as detailed in [SSW04].

Figure 2.1: The Zynq Processing System [Xil18b]

"FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

- 1. RISC Instructions processors have a reduced number of instructions. All instructions can be executed in single clock cycle and each have a fixed length to allow pipeline instruction execution.

- 2. Pipelines Multiple instructions are executed in parallel, each instruction, which participate in the pipeline execute a separate phase of the instruction execution.

- 3. Registers The processor have a large number of general purpose register set. Any register can store data or address.

- 4. Load-Store architecture The processor process only data stored in registers. To transfer data between the register and external memory there are special load and store instructions. This comes from the fact that memory instructions are costly.

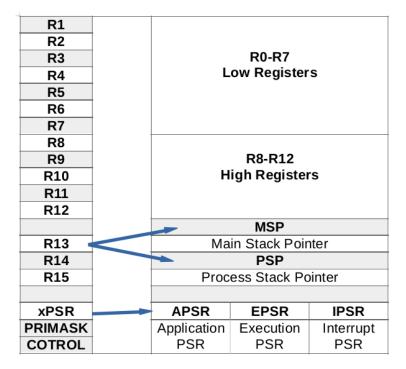

### **ARM registers**

The Cortex A9 processor implements the ARMv7-A architecture that include the following architecture extensions: SIMD architecture for integrated floating-point vector operations; vector floating point computation (IEEE 754 standard); security extension for enhanced security; multiprocessing extensions for multiprocessing functionality ([ARMb]). General purpose registers are available in user mode, which hold data or and address. The register bank contain sixteen general purpose registers plus the special purpose register bank. Figure 2.2 represent a general overview of the registers. In the figure the special registers can differ from the represented one.

Registers R0 - R12 are general purpose registers, which are divided in low registers (R0-R7) and high registers (R8-R12). The low registers can be accessed by any instructions, while the high registers cannot be accessed by some Thumb instructions.

Register R13 is the Stack Pointer records the current address of the stack. R13 it is used for saving the context of a program while switching between tasks. It has to stack pointer (SP) registers. On of SP is the Main stack pointer (MSP), used in applications that require privileged access such as operating system kernel, and exception handlers. The other stack pointer is the Process Stack Pointer (PSP), which is used in base-level application code (when not running an exception handler).

R14 is the Link Register (LR) used to store the return address of a subroutine or a function call.

R15 register is the Program Counter (PC) used to record the address of the current instruction code. It is automatically incremented by 4 at each operation (for 32-bi instruction code). Exceptions are the branching operations. A branching operation, such as a function calls, will change the PC content to a specific address, meanwhile save the current PC to the Link Register. The PC will load the value from LR after a function is finished.

Special register provide information about the program execution status, and provide the ALU (Arithmetical Logical Unit) flags. The xPSR register contains three registers, such as Application PSR (APSR) containing the ALU flags, the Interrupt PSR (IPSR), containing executing interrupt service routine number and the EPSR the Execution PSR (EPSR). For a detailed register description please consult [ARMb] Technical Reference Manual.

Figure 2.2: ARM registers available in user mode

### The Advanced Micro-controller Bus Architecture (AMBA)

For System on Chip architectures there are two bus types: external and internal bus.

| AMBA Family | Bus Protocol | Processor             |

|-------------|--------------|-----------------------|

| AMBA5       | СНІ          | Cortex-A57, A53       |

| AMBA4       | ACE          | Cortex-A7, A15        |

|             | AXI4         |                       |

|             | AXI          | Cortex-A9, A8, R4, R5 |

| AMBA3       | AHB          | Cortex-M0, M3, M4     |

|             | APB          | Cortex-M0, M3, M4     |

|             | ATB          |                       |

| AMBA2       | AHB, ATB     | ARM7, ARM9            |

| AMBA1       | ASB, APB     |                       |

#### Table 2.1: ARM AMBA bus types and examples

The external bus connects off-chip memory, and other external devices. The Zynq processing system has an external memory interface to connect external memories such as DDR2, DDR3 and other newer memory types. In this way the user do not have to care about external memory interfacing. The internal bus connects internal components inside the chip. This bus is known as system bus with internal bus characteristics, which depends only by the programmable interconnections. The ARM processor cores have standardized bus interface architecture called also AMBA bus. This specification is intended to implement the on-chip communication interface. The AMBA standard is an open standard on-chip specification. The internal bus is the standard interface that enables Intellectual Property (IP) re-use and facilitate the development of multi-processor designs. Table 2.1 defines the AMBA bus protocols. Since the SOC Zynq architecture use AXI bus protocol, here we just enumerate all the other AMBA bus protocols in order to get an idea about what their acronym means:

- The AMBA5 CHI (Coherent Hub Interface) specification defines the interfaces for the connection of fully coherent processors.

- AMBA4 ACE Coherency Extensions (ACE) extends AXI with additional signaling introducing system

wide coherency.This system coherency allows multiple processors to share memory and enables

technology like ARM's big.LITTLE processing. The ACE-Lite protocol enables one-way aka IO coherency, for example a network interface that can read from the caches of a fully coherent ACE

processor [KS13].

"FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

- AMB AXI Advanced is part of the ARM Advanced Micro-controller Bus Architecture AXI3 and AXI4 specifications [ARMa] is a parallel high-performance, synchronous, high-frequency, multi-master, multi-slave communication interface, mainly designed for on-chip communication. AXI offers a wide spectrum of features, including:

- separate address/control and data phases;

- support for unaligned data accesses;

- burst-based transfers, with a single transmission of the starting address;

- separate and independent read and write channels;

- support for outstanding transactions;

- support for out-of-order transaction completion for transactions having different thread IDs on the same master port. Transactions on the same master port that have the same thread ID must be completed in order. Additionally, different master ports may be completed out of order with respect to each other.

- support for atomic operations.

- AHB Advanced High-performance Bus is a bus protocol introduced in Advanced Micro-controller Bus Architecture. A simple transaction on the AHB bus consists of an address phase and a subsequent data phase. Access to the target device is controlled through a non-three-state multiplexer, for this reason only one bus-master is allowed at a time. Allows development of embedded systems in FPGA.

- APB Advanced Peripheral Bus is a low cost interface optimized of low power consumption and reduced interface complexity. The APB interface is a simple, synchronous protocol. It is not a pipeline protocol.

- ATB Advanced Trace Bus defines how a trace information transfers between components in a trace system. The ATB interface supports various features, including: stalling of data, using valid and ready responses, control signals that indicate the number of bytes valid in a cycle, identification of the originating component, by signaling an associated ID with each data packet, support for any trace protocol information, data information or data format requirements, identification of data from all originating components, flushing.

### ARM Cortex-A9 Processor Micro-Architecture

Based on the ARM documentation [ARMb] ARM Cortex A9 processor instructions has a speculative outof-order speculative issue super-scalar execution 8-stage pipeline giving 2.50 DMIPS/MHz/core [ARMb] each core processing. The NEOM co-processor technology allows SIMD operation, and floating point unit accelerate the floating point operations with twice speed of the previously ARM FPU version. THUM2-2 instruction set increase code density without influencing the instruction execution speed

"FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

compared to the performance of ARM 32 bit instruction performance. The processor implements the ARMv7 Debug architecture that includes support for TrustZone and CoreSight. The Cortex-A9 processor implements Baseline CP14, Extended CP14 debug access, and memory mapped access to the debug registers. See [ARMb] for more detailed in formations.

## 2.3.2 Memory interfaces

The Xilinx Zynq SOC and 7 series FPGAs with a "Memory Interface Solution" core with its memory controller and physical layer core (PHY) optimize interfacing for user designs using the AMBA standard Advanced eXtensible Interface (AXI4) slave interfaces to DDR3 and DDR2 SDRAM devices and other. Using the Memory Interface Generator (MIG) IP one can easily interface external memories. One can setup the clock ratio, the power supply voltage for the respective FPGA IO banks, setup the memory type, memory part, data width and etc. Also the IP can create a custom memory controller part.

### 2.3.3 Processing System Interconnect

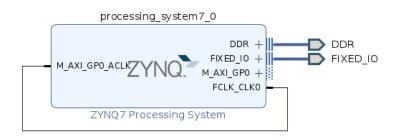

The processing system interconnect provide an interface between the PS (Processing System) and PL (Programmable Logic). The interconnect features are as follows: Enable/Disable I/O Peripherals (IOP), Enable/Disable AXI I/O ports, MIO Configuration, Extended Multiple Use I/Os (EMIO), Accelerator coherency port (ACP), Transaction checker (ATC), Interconnect logic for Vivado Design Suite IP – PS interface, PL Clocks and Interrupts, PS internal clocking, Generate PS configuration register.

## 2.3.4 Memory Map

The Cortex-A9 processor uses 32-bit addressing. PS peripherals and PL AXI slave interfaces are memory mapped to the Cortex-A9 processor cores. All AXI slave PL peripherals will be located between the addresses:

- 4000\_000 and 7FFF\_FFFF connected to AXI GP0 interface and

- 8000\_0000 and BFFF\_FFFF connected to AXI GP1 interface.

Note that the Zynq 7000 have different memory resources. First the primary memory is the On-chip memory (OCM), which is the RAM and Boot ROM. Second resource of memory is the off chip memory, which is connected via the MIG controller (DDRx dynamic memory controller), which supports LPDDR2, DDR2, DDR3. Third resource is the Flash/static memory controller, which supports SRAM, QSPI, NAND/NOR FLASH.

## 2.3.5 PS Boots first

After Power-on-Reset (POR) the PS clock is enabled. Then, the PS begins executing the BootROM code in the on-chip ROM to boot the system. The POR resets the entire device with no previous state saved.

"FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

The BootRom is the first software run in the application processor unit. The BootROM executes on CPU 0 and CPU 1 executes the wait-for-event (WFE) instruction. The boot device can also hold a bitstream to configure the PL and an embedded operating system, but these are not accessed by the BootROM code. The bitstream and the operating system are stored in the flash memory (external memory). In master boot mode the system boots from the flash device, while in JTAG boot mode, the BootROM code does minimal system configuration and enables a JTAG interface. After the BootROM executes, the First Stage Boot Loader (FSBL)/User code takes control of the PS and is able to further configure the device, including the PL. For further details and reading please see Xilinx User Guide UG821 and [Xil21].

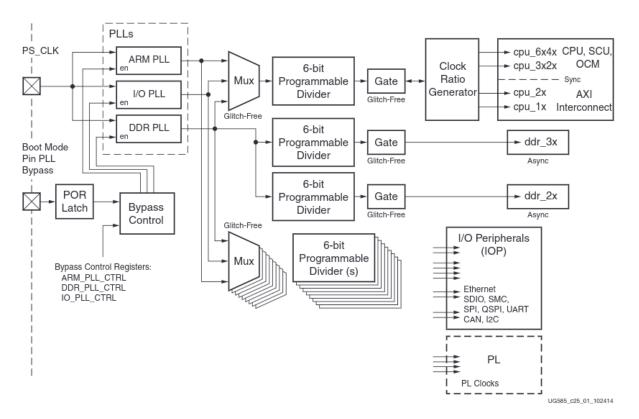

## 2.3.6 Clock resources

The external clock source for the PS drives the PS clock subsystem, which are derived from one of three programmable PLLs: CPU, DDR and I/O. Each of these PLLs is loosely associated with the clocks in the CPU, DDR and peripheral subsystems (see figure 2.3). The PLLs generates the corresponding clock for the SPU, DDR and peripherals, also contains four clock generators for the PL. The clock generation paths include glitch-free multiplexers and glitch-free clock gates to support dynamic clock control. The 6 bit programmable dividers helps to generate the corresponding clock frequency together with the Clock Ratio Generator.

## 2.4 Summary

This chapter gave a summary about the Zynq processing system. It was presented the ARM processor in general and was summarized the AMBA bus standard and ARM Cortex A9 processor. There were presented the memory interface MIG, the processing system interconnect, memory map and the PS boot sequences.

Figure 2.3: PS Clock subsystem block diagram

# **Chapter 3**

# VHDL hardware description language

## **3.1** Introduction to Hardware Description Language

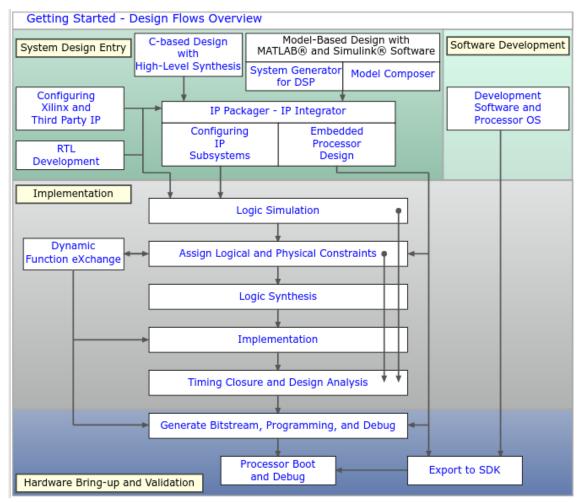

Embedded system design is the process that begins with setting the requirements for the system and goes through several steps to the physical implementation of the system. With the development of integrated circuit technology, can be implemented extremely complex embedded systems. Dealing with complex designs has resulted in different trends in design methods:

- Behavioral method: It specifies the system in terms of its expected behavior. It is the closest to a natural language description of the circuit functionality, but also the most difficult to synthesize.

- Structural design style: The system is specified in terms of lower level components (in this case logic gates), functional blocks connected with internal signals. The translation of such a specification into a physical circuit is straightforward.

- Data-flow method: This design style is similar to logical equations, although in general is not limited to logical values only. The specification is comprised of expressions made up of input signals and assigned to outputs. In most cases such an approach can be quite easily translated into structure and the implemented.

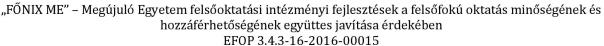

In the design process, simulations are complementary activities of the synthesis (see figure 3.1). In the case of application specific integrated circuits (ASIC) or embedded systems design; for example, simulations eliminate design errors and thus significantly reduce manufacturing costs (ex. production of integrated circuit masks or printed board circuit – PCB or Field Programmable Gate Array – FPGA – design). Extensive simulations can result in 82% of bug elimination and 9 hours saved by finding each defect, also increase productivity. shows the correspondence between design steps and simulation steps during the development process. The first step is to define the the system requirements. These requirements specify operating speed, delay times, connection points (interfaces), dissipated power, and other physical parameters.

Figure 3.1: Design flow of digital systems

Based on the requirements mentioned above, the system is designed during the functional design and the functional requirements can be checked with the simulation used at this level. This design can be refined at the register transfer level. At this level, the tasks are taken over by registers, memories, arithmetic units, state machines. Logical design implements the elements defined at the register transfer level. The verification, debug simulation also models the design errors expected during production and the design errors induced by environmental influences. Finally, the physical implementation creates the digital circuit, which can even be a ready-to-manufacture integrated circuit or system.

## 3.2 Hardware Abstraction Levels

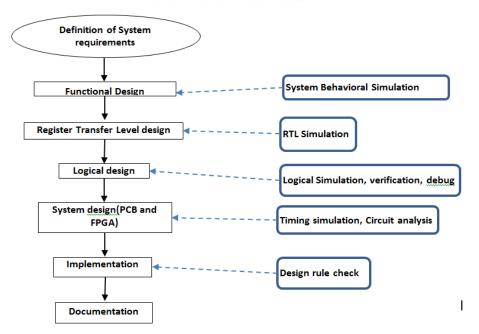

At each level of the design hierarchy, we describe the system design using circuit elements. Complex digital systems are described in different ways. However, these description methods are compatible with each other . Circuits are generally described in three domains: a behavioral domain, structural domain and a physical domain. These description methods are expressed in the Y diagram represented in figure 3.2.

Figure 3.2: Y chart [GD99] p. 358

Gajski has developed the Y chart in VLSI (Very Large Scale Integrated Circuits) and Kuhn in the year 1983 to categorize the behavior of hardware designs based on the three different domains [[GK83]]. The three different domains are behavioral, structural and physical/geometry domain, which are on radial axis. Each of the corresponding domains can be further divided into levels of abstraction using concentric rings and each of the domains falling within the circle forms a group and keep going on in a top down fashion towards the center of the core.

#### 3.3 Textual description of digital systems

Technology development and growing complexity of integrated circuits resulted in that conventional schematic design methods has become increasingly opaque and difficult-to-manage the design. Circuit technology has made it possible to manufacture so-called programmable logic circuits (as mentioned

"FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

before). However, designing with programmable logic devices required a design tool that allows the user easily describe the objective functionality of the design. First, this description method was elaborated in the description of the fuse map file resulting from the circuit technology. The fuse map defined the connections inside the circuit, similar to the net list used in schematic designs. This method was cumbersome and complex, so it became necessary to develop a general hardware modeling language capable of uniformly describing digital circuits at different levels of abstraction to design a variety of usable electronic systems using programmable circuits from different manufacturers and implemented with different technologies. The technology evolution resulted in different text based hardware description languages such as: PALASM, ABEL, VHDL, VERILOG, System C, etc. In our days the most known hardware languages are VHDL, System Verilog and C or C++ based hardware description languages (such as SystemC, Catalpult C and others). In the following are presented shortly the most known hardware description languages and the VHDL is presented in detail.

## 3.3.1 VHDL hardware description language

What means the double acronym VHDL? The meaning of the VHDL is: VHSIC-HDL – (Very High Speed Integrated Circuits Hardware Description Language). Originally the VHDL was developed by the USA DoD (DoD – Department of Defense). The development result was a hardware description language, which highly satisfied all expectation of system design requirements. The VHDL is a self-documenting, structured and understandable language. The source code in the meantime is also a kind of specification document. The most important part of HDL (hardware description language) is the parallelism and the concurrent process handling. In addition, HDL can handle complex and compact sequential circuit models. The standardization of VHDL was made in 1987 by the IEEE (Institute of Electrical and Electronics Engineers). The first official standard of VHDL was elaborated in 1993. The VHDL extension to analog and mixed signal systems modeling opened a new chapter in the electronic system design and modeling. VHDL-AMS (analogue mixed signal) is an extension of the VHDL. The extension is valid for systems model simulation, because the analog circuit synthesis is a very complex and many parameter problem, which is not solved yet.

## 3.3.2 Verilog hardware description language

The designers of Verilog HDL (Gateway Design Automation – 1984) intention was to create a C like hardware description language, since the C programming language is already spread in the micro processing development applications. Verilog is sensible to lowercase and uppercase letters. Similar to ANSI C/C++ has pre-processing, flow control instructions (if/else, for, while, case, etc.) and is compatible to precedence operators. Syntactical differences are in the variable typed declarations, process module separation and others. A design written in Verilog program has multiple hierarchical modules. The modules contain the design hierarchy. The connection between the modules give the ports (input, output, inout) A module can contain internal signal declarations (such as wire, reg, integer, etc.), sequential blocks, modules Verilog is a simultaneous and synchronous data-flow processing language.

"FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

### 3.3.3 SystemC hardware description language

"SystemC is a set of C++ classes and macros which provide an event-driven simulation interface (see also discrete event simulation). These facilities enable a designer to simulate concurrent processes, each described using plain C++ syntax. SystemC processes can communicate in a simulated real-time environment, using signals of all the data types offered by C++, some additional ones offered by the SystemC library, as well as user defined. In certain respects, SystemC deliberately mimics the hardware description languages VHDL and Verilog, but is more aptly described as a system-level modeling language." (Wikipedia) SystemC<sup>®</sup> is an extension of the ANSI C++ class library for hardware design. The purpose of SystemC to give a C++ based design service for hybrid systems, where both hardware and software elements can be found.

The language is described by the IEEE 1666-2005 standard. During a SystemC application one can use the possibility of C++, but with the constraints that are in the standard definitions.

## 3.4 VHDL basics

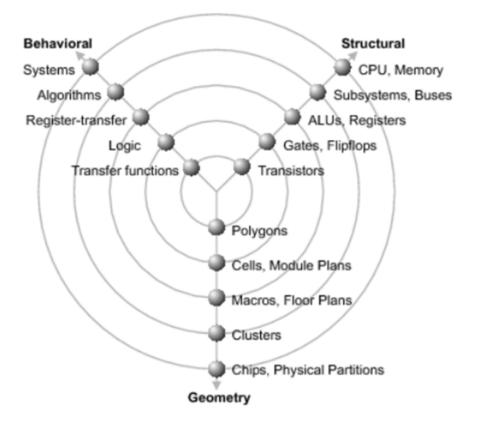

Let us analyze the structural and behavioral system description in more detail. A digital system is basically used to process signals. Signals can take binary values (0 or 1, X, Z, etc.). The elements of a digital system are components such as logic gates, flip-flops, counters, processors, and so on. The connections between the components are made by wires. The input signals are also converted by the components (by the logical functions) into output signals, but there are bidirectional or input-output signals also. A VHDL program from the point of view of its structure consists of design units. A feasible (synthetitsable) VHDL program should contain two design units: one *entity* and one *architecture* unit. The *entity* is the interface to the block of hardware, while the *architecture* defines the system internal structure or the system behavior. An *entity* may have several alternative *architecture* (see figure 3.3).

Figure 3.3: VHDL model

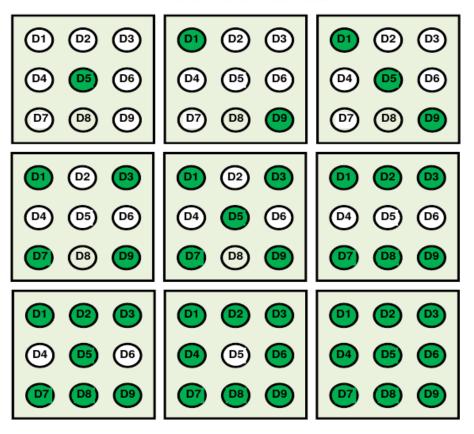

Figure 3.4: Domino code display

The structure of a VHDL program can best be illustrated through an example. Let us consider the example of the so cold "domino code display" (see figure 3.4). The output of the domino code will be 9 LEDs organized as seen in figure 3.4. In the classical digital systems first one should write the truth table, then using Boolean algebra and Karnaugh maps, then minimize the logical equations and finally implement the circuit. The result of the Boolean minimization is given by:

$$D1 = D9 = D + C + B; D2 = D8 = D + C * B; D3 = D7 = D + C; D4 = D6 = D; D5 = A;$$

(3.1)

where the "+" is the logical **OR** and the "\*" symbolize the logical **AND** function, **D**, **C**, **B**, **A** are the input signals (variables) and **D9**, **D8**, **D7**, **D6**, **D5**, **D4**, **D3**, **D2**, **D1** are the output functions. See figure 3.4). The "domino coder" solution given in VHDL code is shown in figure 3.5.

Let us explain the domino VHDL code implementation presented above, and introduce the basic elements of a VHDL program (such as entity, architecture).

#### "FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

| 19 🔆                                          |                         |                                                         |

|-----------------------------------------------|-------------------------|---------------------------------------------------------|

| 20                                            |                         |                                                         |

| 21                                            |                         |                                                         |

| 22 library IEEE;                              |                         | open library IEEE                                       |

| 23 use IEEE.STD LOGIC 1164.ALL;               |                         | open standard logic package                             |

| 24                                            |                         |                                                         |

| 25⊜ entity domino is                          |                         | entity name: domono;                                    |

| 26 🖯                                          |                         | entity begins here;                                     |

| 27 🤤 generic (nr point domino: in             | teger := 10 );          | <ul> <li>generic is not used in this example</li> </ul> |

| 28 Port ( D : in STD LOGIC:                   | •                       | input port definition D                                 |

| <pre>29 C : in STD LOGIC;</pre>               |                         | input C                                                 |

| 30 B : in STD LOGIC;                          |                         | input B                                                 |

| 31 A : in STD LOGIC;                          |                         | input A                                                 |

| 32 domino : out STD LOGI                      | C VECTOR (9 downto 1)); | output port                                             |

| 33                                            | -                       | output port definition is vector of 9 bits              |

| 34⊖ end entity domino;                        |                         | end entity domino                                       |

| 35                                            |                         | ,                                                       |

| 36 🖯 architecture Behavioral of domin         | o is                    | architecture description begins here                    |

| 37                                            |                         |                                                         |

| 38 begin                                      |                         |                                                         |

| 39                                            | description of outp     | ut functions                                            |

| <pre>40 domino(1) &lt;= D OR C OR B;</pre>    | DOMINO led 1            |                                                         |

| <pre>41 domino(2) &lt;= D OR (C AND B);</pre> | DOMINO led 2            |                                                         |

| <pre>42 domino(3) &lt;= D OR C;</pre>         | DOMINO led 3            |                                                         |

|                                               | DOMINO led 4            |                                                         |

|                                               | DOMINO led 5            |                                                         |

| <pre>45 domino(6) &lt;= D;</pre>              | DOMINO led 6            |                                                         |

| <pre>46 domino(7) &lt;= D OR C;</pre>         | DOMINO led 7            |                                                         |

| <pre>47 domino(8) &lt;= D OR (C AND B);</pre> | DOMINO led 8            |                                                         |

| 48 domino(9) <= D OR C OR B;                  | DOMINO led 9            |                                                         |

| 49                                            |                         |                                                         |

| 50                                            |                         |                                                         |

| 51 end Behavioral;                            | end architecture de     | scription                                               |

| ro -                                          |                         |                                                         |

Figure 3.5: Domino coder implemented in VHDL

## 3.4.1 Entity as the interface model

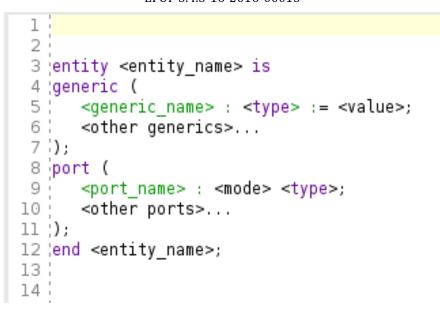

The *entity* defines the design name and the way that the described VHDL element how is connected to other elements, the circuit unit's basic parameters, input and output pins. That is, with what static parameters (constants) and dynamic channels (signals) happens the information exchange between the *entity* and its environment. The *entity* allows defining any parameters that are passed into the model using hierarchy. The basic template for an entity is shown in figure 3.6.

Signals defined with the *port* section can be used to connect entities together. In the domino example 3.5 the entity contains four input signals (D, C, B, A) and a 9 bit bus output (D[9:0]). The schematic symbol is much more expressive (see figure 3.7). The textbf*port* declaration defines the type of connection, direction, and dimension. A textbf*port* direction can be *in* (only read), *out* (only write) and *inout* (read and write). Port type is *bit (std\_logic)* or *bit\_vector (std\_logic\_vector)*. The type bit\_vector defines buses. If the model has parameters, then this are defined by using the keyword *generic*. Generic declaration is similar to that of constant. A *generic* definition should contain type (integer, time) and initial value defined after the symbol":=""."

## 3.4.2 Architecture as model functionality, behavior, structure

There is no *architecture* without an interface. Its importance is so great that *architecture* is specified in VHDL as the architecture of entity (see domino implementation above figure 3.5). The general structure of the architecture is shown in 3.8. The first line of the architecture links the implementation to the

"FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

Figure 3.6: Entity template

Figure 3.7: The domino coder schematic created from VHDL code

entity defined above (architecture Behavioral of domino is).

VHDL architecture can have a variety of structures to achieve different type of functionality (from simple combinatorial to complex sequential or structural description). Declarative items can be internal signals seen only in the architecture, or other components described by other VHDL models.

```

1

2

3 architecture <arch_name> of <entity_name> is

4 -- declarative_items (signal declarations, component declarations, etc.)

5 begin

6 -- architecture body

7 end <arch_name>;

8

```

### Figure 3.8: Architecture structure

### 3.4.3 Constants and Signals

When a value needs to be static throughout a simulation, the type of element to use is a **constant**. A **constant** is used to initialize parameters, registers, or other. **Signal**s are the "wires" inside the architecture connects processes or design elements (components) together. **Signal**s have no direction they are read-and-write type. **Constant**s and **signal**s are declared in the architecture before the **begin** statement.

### 3.4.4 Packages, Libraries

Design units are the building blocks of the VHDL program. When compiling a VHDL program, the processing program distinguishes five separate program units. Each unit is analyzed separately. The five separate units are:

- entity,

- architecture,

- package definition,

- package body,

- configuration.

The entity and the architecture were presented previously. The *package definition* describes the elements implemented and usable in the package, while the *package description* includes equations describing the implementation of functions, components, VHDL program codes, and so on. One characteristic of VHDL is that multiple architectures can be assigned to an entity. The *configuration* specifies which architecture is assigned to the design entity under the conditions we defined. The VHDL *library* stores the design units that contain the most commonly used components and functions. To achieve rapid synthesis, the IEEE created various standardized VHDL *packages*, which were defined in standards 1164, 1076.3. (The actual standard is IEEE 1076-2008). Standard libraries are opened with the *library* keyword, while the library package you want to use is specified with the *use* keyword.

Opening a library and assign packages within a VHDL program is necessary because one can use in the given VHDL program different data types defined in the packages. For example: standard logic (std\_logic), standard bus system (std\_logic\_vector), which is part of the std\_logic\_1164 package.

> library IEEE; use IEEE.STD\_LOGIC\_1164.ALL; use IEEE.numeric\_std.all; use IEEE.std\_logic\_unsigned.all;

-- open library IEEE -- open standard logic package -- commonly used packages

Figure 3.9: Open IEEE Library and use packages

## 3.4.5 VHDL grammar and lexical elements

Lexical elements are the syntax units that form the basis of the VHDL language. These include comments, identifiers, reserved words, numbers, characters, and strings. The *comment* is text after two minus signs ("--"). The comment is ignored when processing the program. The comments are mainly used to document the program. A well commented program documenting itself. *Identifier* is the name of a VHDL object. The following rules apply to identifiers:

- only Latin letters are allowed;

- decimal numbers and underscore can be used to name the identifier;

- the first character of the identifier is always a letter;

- the last character cannot be an underscore ("\_")

The last character cannot be an underscore ("\_") Correct examples for identifiers: A10, next\_state, NextFunction, etc. VHDL is not case sensitive; the following identifier names all refer to the same object: identifier, IdENTIFIER. Therefore, the correct programming mode is to always refer to an object in the same way. Best practice for identifier names is to use expressive names as possible, but the use of reserved words is forbidden!

**Numbers, characters and strings:** In VHDL, the type of numbers can be integer, floating point, real. In the representation of numbers, the decimal number system (i.e. 23), the double precision system (i.e. 23 => 2 #10111#) or the hexadecimal system e.g. (23 => 16#17#) is used. For example, the number 123456 is the same as the number 123\_456, just as the binary number 2#10100101101# is the same as the number 2#1010\_0101\_1010#.

*Character* types are denoted by apostrophes, such as 'V', 'H', 'D', 'L'. Note that the 23 and '23' are different, the first is a number and the second is a character type. Character strings or strings are enclosed in double quotation marks, such as "VHDL". Note that the number 2 # 0101\_1010 # and the character lines "0101\_1010" also differ in terms of notation and content, what's more, the following two character lines are not the same: "0101\_1010", "01011010".

### 3.4.6 VHDL Objects

An object is a data type which contains a given value. Four object types are known:

signal

- variable

- constant

- file

The file type is not discussed in this chapter because it is not a synthesizable element.

A *Signal* must be defined at the beginning of the architecture (after "architecture", before "begin"). The signals are only visible in the architecture which defined them. The *signal* definition is as follows: signal <name> : <type> := <value>;

signal a signal name: std logic := '0';

The value of the signal is assigned by the following operator: <= Example:

a\_signal\_name <= d\_in0 and din1;

*Variable*s in the traditional sense play the same role like variables in programming languages. The use of variables is only allowed in *processes*. The variable can also be thought of as a "local symbolic storage element" to describe the abstract behavior of the system. The variable is defined as follows:

variable <name>: <type> := <value>; - variable declaration

The value of a variable is assigned by the following operator :=; Example:

variable name\_of\_var: std\_logic\_vector(2 downto 0) := "00"; - variable with init value "00"

name\_of\_var := in1 and in2;

**Note:** Because the compiler does not assign any timing values to a variable, means that assigning a value to the variable has an immediate effect on it.

*Constant* The value of the constant cannot be changed in the VHDL code. The constant is defined as follows:

```

constant <name>: <type> := <value>;

constant bus_dimension: integer := 32;

```

## 3.4.7 Data types and operations

In the VHDL language, we assign to each variable a data type (i.e. object or signal). The data type defines a set of values that variables can take and a set of operations that can be performed with the variables. Because in VHDL the values that can be assigned to signals and the operations that can be performed on them are strongly type-dependent, type conversion should be applied if other data type is assigned to a a given object.

### Standard VHDL data types

From the synthesis point of view, the most common data types are as follows:

• integer in VHDL the integer type has a 32 bit representation and can get values in the  $[-2^{31}, 2^{31} - 1]$ . VHDL defines two sub types such as normal type ( $N^*$ ) and positive (N) type;

29

• Boole type with true, false values;

- **bit** type with '0', '1' values;

- **bit\_vector** type defined as a multi bit signal.

In the case of real digital design, a signal can be assigned with many signal levels not only with twostate signal levels, as a signal can be in a high-impedance state or even can have a signal level conflict in the case of wired logic. Therefore, in the VHDL, the STD\_LOGIC and STD\_LOGIC\_VECTOR types were introduced in the IEEE std\_logic\_1164 package to solve this problem. This data types allows a more flexible signal handling.

### STD\_LOGIC, STD\_LOGIC\_VECTOR data types

The most commonly used two data types are contained in the *STD\_LOGIC\_1164* package. The *std\_logic* type is a sub type of the unsigned *std\_ulogic* contained in the *STD\_ULOGIC\_1164* package. For use of any data type, first the library and then the package must be opened: library IEEE;

### use IEEE.STD\_LOGIC\_1164.ALL;

The std\_logic data type can have nine possible values: {'U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-'}. These values are explained as follows:

- '0' and '1' denote the values "definite logic 0" and "definite logic 1", respectively, which are taken by a signal driven by standard circuit;

- The high impedance value 'Z' can be taken by the signal if the drive circuit is a tri-state buffer;

- 'L' and 'H' 'weak logic 0' and 'weak logic 1' can be set to a signal for wired logic circuits when the driver circuit provides a weak drive current;

- 'X' and 'W' "indeterminate logic state" or "weak indeterminate logic state" value taken when the driver signal value cannot be interpreted as a logic 0 or a logic 1. This state occurs when two output drivers control the signal to a logic state of conflicting values (logic 0 and 1). This is happen especially in circuit simulation conditions indicate faulty circuit operation, especially in circuit simulation. • 'U' - Status used in simulation. Indicates that a value has not yet been assigned to the signal or variable. • '-' indicates that the signal is redundant.

## 3.5 Behavioral system description in VHDL

### 3.5.1 Combinational Signal Assignments

There is a strong relationship between the signal assignments and VHLD, as result there can be achieved very effective implementations. In the VHDL standard there are three type of simultaneous/parallel signal assignments (see example in 3.10):

• Simple signal assignment, which correspond to the Boolean algebraic equations;

- Conditional signal assignment;

- Selected signal assignment.

Digital circuits are combinational and sequential type. Combinational circuits do not have internal storage elements (memory) and internal intermediate states. The output function of the combinational system has always the same value for a given variation of the input signals. In reality, short transients may appear due to the gate delay of the circuits. However, when the input variables are steady state, the output always take the same value. From the point of view of implementation (with programmable logic circuits) the combinational circuit is without memory or internal storage (latch or flip-flop) or without feedback.

- simple signal assignment with Boolean functions:

The signal assignment ""<=" means that the input signal value is assigned immediately to the output (see figure 3.10).

- Conditional signal assignment

The outputs get the input values based on the *when ... else* condition (see figure 3.10).

- Selected signal assignment

This type of signal assignment is similar to the truth table. The selector usually is a *std\_logic\_vector*, when the value what gets the selector is true then the given values is assigned to the output signal. The closing operator *when others* assign an output values for all other input signal variations, which are not enumerated (see figure 3.10).

### 3.5.2 Sequential signal assignments

The outputs of sequential circuits are a function of the state of the input variables and the actual value of the internal variables (state register output values). The description of sequential system can be done by concurrent assignments, but this is not the common method. The **process** is the sequential description mode used for description of sequential systems, state machines, etc. The process is the mechanism by which sequential statements can be executed in the correct sequence, and with more then on process, concurrently. A process consist of a sensitivity list, declarations and statements. The process is executed simultaneously with the parallel assignments, however, the program lines in the process take place sequentially after a signal from the sensitivity list activate the process (change of signal). In the process execution an important role plays the signal identities, conditional signal assignments ("if then else", "case"), and cycles. It is important to clarify the difference between sequential signal assignment and a sequential logic circuit. The first one describes the process internal state while the last one is the digital circuit with internal states. Note that a process can implement not only sequential circuit but also combinational one.

The signals from the sensitivity list (see figure 3.11; "all\_input\_signals,separated\_by\_commas, "clk" and "rst") activate the process. If at least one signal change its state the process is executed.

"FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

> 34⊜॑ entity sig\_assign is 35 Port ( a : in STD\_LOGIC; 36 b : in STD\_LOGIC; 37 c : in STD LOGIC; 38 d : in STD LOGIC; 39 s : in STD\_LOGIC\_VECTOR (3 downto 0); 40 f0 : out **STD\_LOGIC**; 41 f1 : out STD\_LOGIC; f2 : out STD\_LOGIC\_VECTOR(6 downto 0)); 42 44 ⊖ architecture Behavioral of sig\_assign is 45 signal for input data bus definition signal d\_in: std\_logic\_vector (3 downto 0); 46 begin 47 48 🖯 -- data bus from input signals -- d in <= d & c & b & a; 49 50 🖨 -- simple signal asignament with Boolean functions: f0 <= a and (b or c) and d; -- simple assignment with "<=" 51 52 © 53 <u></u> conditional signal assignment 54 f1 <= a when s = "0000" else -- if s = 0 then f1 <= a else b when s = "0001" else 55 -- if s = 1 then f1 <= b else c when s = "0010" else -- if s = 2 then f1 <= c else 56 57 d : -- if s = any other value then f1 <= d 58 O 59 -- selected signal assignment 60 🖻 the example is a seven segment decoder example 61 with s SELect f2 <= "1111001" when "0001", 62 "0100100" when "0010", 63 - -2 "0110000" 64 when "0011", - -3 "0011001" 65 when "0100" - -4 "0010010" when "0101" 66 - - 5 "0000010" "0110" 67 when - - 6 "1111000" when "**0111**" 68 - - 7 "0000000" 69 when "1000" - -8 "0010000" 70 when "1001" - -9 71 "0001000" when "1010" - - A "0000011" when "1011" 72 - - h 73 "1000110" when "1100" - - C "0100001" when "1101" 74 - - d "0000110" when "1110", 75 - - F "0001110" when "1111", 76 - - F "1000000" when others; 77 - - 0 78 🖨 end Behavioral; 79

Figure 3.10: Combinational Signal Assignment Methods

#### Variables

Definition of internal *variables*, used by the process, which are local signals, objects can be seen only inside the process. As the process is activated the sequential signal assignments are executed one-by-one and the process transits to the next internal state. A process as part of a digital systems can be in active or suspended state. Inside the process, signal assignment is done line by line execution of the process body. Signal use inside the the process is done taking into account three important aspects:

#### "FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

```

34⊖ entity example_proc is

35

generic (dim: integer := 16);

Port ( all_input_signals: in STD_LOGIC_VECTOR (dim-1 downto 0);

36

37

separated_by_commas: in STD_LOGIC;

38

clk : in STD_LOGIC;

-- clock

39

rst : in STD_LOGIC); -- reset

40 \stackrel{.}{\ominus} end example_proc;

41

42  ⇔ architecture Behavioral of example proc is

43

44

begin

45

- combinational process example

46 process (all_input_signals, separated_by_commas)

47 begin

48

<statements>;

49 \doteq end process;

50

-- sequential process with negative edge clocked

51

-- and synrconous High reset

52 process (clk)

53 begin

54 ė

if (clk'event and clk = '0') then

55

-- if there was a change in the clock signal and its value = 0

-- this define the negative edge

56

if rst = '1' then

57 ė

58

-- if reset is 1 then execute the reset statments

59

-- <statements>;

60

else

61

-- otherwise

62

-- <statements>:

63 ė

end if;

64 🖨

end if;

66

-- sequential process with positive edge clocked

67

-- and synrconous Low reset

68 process (clk)

69 begin

70 👳

if (clk'event and clk = '1') then

71 <del>\</del>

if rst = '0' then

-- <statements>;

72

73

else

74

<statements>;

75 🖻

end if;

76 <u></u>

end if;

77 🗄 end process;

78 end Behavioral;

```

#### Figure 3.11: Example of different process types

- signal definition in process is forbidden;

- signals take the new value assigned in the process became valid at the process termination. Signals preserve their previous values until the process termination;

- in the case of multiple assignments for the same signal the last value is preserved at process termination.

| 34⊖ entity var example is                |                                      |

|------------------------------------------|--------------------------------------|

| 35 Port (a : in STD LOGIC; in            | put signals a, b, c                  |

| 36 b : in STD_LOGIC;                     |                                      |

| 37 c : in STD_LOGIC;                     |                                      |

| <pre>38 f_out : out STD_LOGIC);</pre>    | output function f_out                |

| 39⊜ end var_example;                     | · –                                  |

| 40                                       |                                      |

| 41 architecture Behavioral of var_exa    | mple is                              |

| 42                                       |                                      |

| 43 begin                                 |                                      |

| 44 🗇 process (A, B, C)                   |                                      |

| 45 variable declarations var1,           | var2, var3                           |

| 46 variable var1, var2, var3: <b>std</b> | _logic;                              |

| 47 begin                                 |                                      |

| 48 var1 := c;<br>49 var2 := var1 and a;  | var1 = c see schetic figure          |

| 49 var2 := var1 and a;                   | on schematic f_out2_i                |

| 50 var3 := var2 nand b;                  |                                      |

|                                          | ; on schematic f_out1_i and f_out0_i |

| 52 ⇔ end process;                        |                                      |

| 53 🖕 end Behavioral;                     |                                      |

Figure 3.13: Schematic resulted from variable assignment example

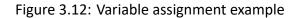

Since signals preserve the last value assigned to them, for this reason they are not used to store temporal values. On the other hand value assignment is made at process end or when the process is suspended. To solve this problem the term of *variable* is introduced. *Variables* are defined inside a process can store temporal value, and they take the values assigned to them immediately after assignment. Variable value assignment is made with ":=" operator. The following example demonstrate variable usage (figure 3.12).

Figure 3.13 represents the schematic obtained by the example given in figure 3.12. The blue wires represents the variables. Var1 assignment is useless in this form, since the and gate four3\_i input is directly connected to signal c.

#### 3.5.3 **Conditional Decisions in processes**

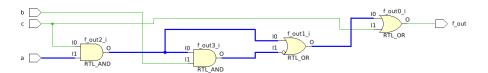

The following decisions can be used only in the process body: IF\_THEN\_ELSE, CASE, for IF\_THEN\_ELSE general structure is represented in figure 3.14. All the possible variants of the IF\_THEN\_ELSE decisions are given in the example (figure 3.15). The figure illustrate by examples the decision possibilities from the basic syntax to the most complete syntax of the conditional assignment.

#### Figure 3.14: IF\_THEN\_ELSE structure

```

41 begin

42 🖯

process(a, b, c, d)

43

begin

44

-- simple IF THEN decision exmple

45 Ö

if (a=b) then

46

f1 <= a;

47 🖨

end if;

48

-- IF THEN ELSE example

49 <del>©</del>

if (a=b) then

50

f2 <= a;

51

-- statments;

52

else

53

f2 <= b;

54

-- more statments;

55 🖨

end if;

-- multiple if condition using genreal form example

56

57 O

if a=b then

58

f3 <= a;

59

statments;

elsif (a>b) then

60

61

f3 <= b;

62

-- more elsif conditions and statments;

63

else

64

f3 <= c;

65

other statments eventualy;

66 <u></u>

end if;

67 👜

end process;

68 end Behavioral;

```

#### Figure 3.15: IF\_THEN\_ELSE examples

#### CASE

As demonstrated above with the if statement is simple to define multiple conditions but for complex

"FŐNIX ME" – Megújuló Egyetem felsőoktatási intézményi fejlesztések a felsőfokú oktatás minőségének és hozzáférhetőségének együttes javítása érdekében EFOP 3.4.3-16-2016-00015

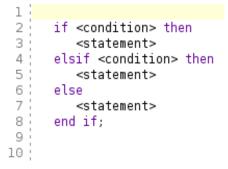

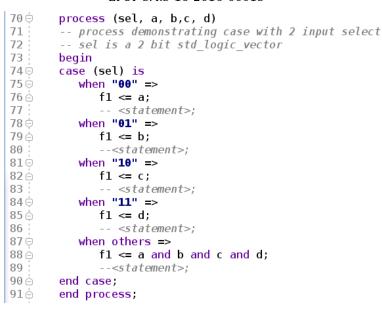

branching the solution is the case structure without having to use Boolean conditions in every case. This structure is useful for state machine description or any other special state transitions. An example of the **CASE** structure is presented in figure 3.16, where four possible choices are presented. **Note** that for a complete description **CASE** structure the termination "**others** should be included (as shonw in figure 3.16)! Figure 3.17 is a case example where the selector line sel is a two bits vector and

```

1

2

case (<2-bit select>) is

З

when "00" =>

4

<statement>;

when "01" =>

5

6

<statement>:

7

when "10" =>

<statement>:

8

when "11" =>

9

<statement>:

10

when others =>

11

<statement>;

12

13

end case:

14

15

```

Figure 3.16: CASE structure

depending on sel value the output f1 is assigned with the values of input signals a, b, c and d respectively.

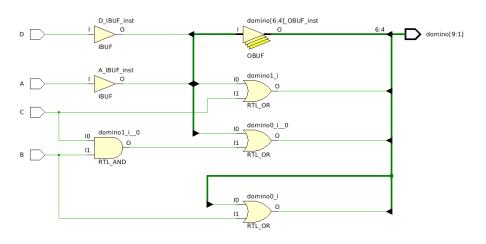

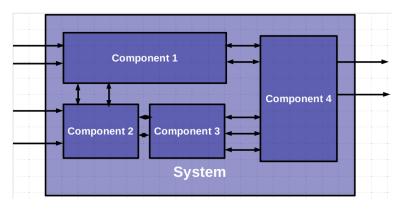

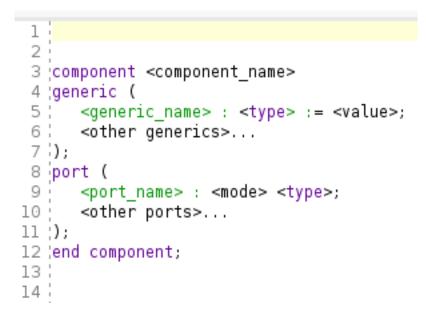

# 3.6 Structural description in VHDL

Structural description for a digital system means describing what components the system consists of and how these components are connected to each other. The structural description allows the application of multi-level (hierarchical) design in the VHDL program using the *component*. Components can be used in the subsystems of a system (in other words in the main VHDL program) that implement even simpler functions. At the lowest level, the VHDL program describes the component in terms of its behavior. The components are connected with signals in the VHDL program. As represented in figure 3.18 the

Figure 3.17: CASE structure example

system is built from components, which are connected with signals (arrows at both end), while the input and output ports represented by unidirectional arrows. In order to connect a component first should be declared (figure 3.19) then instantiated (figure 3.20). A *component* needs two VHDL elements for the structural description. First the *component* is described in as a stand-alone entity - a VHDL program - that has a stand-alone entity and architecture. Secondly the *component* should be declared then instantiated. *Component* declaration makes the connection to the original VHDL module with the definition of its entity (generics and ports) while *Component* instantiating defines the relationship of the *component* ports and other signal from the architecture where the component was invoked. Steps to insert the part:

- 1. Component behavior design in VHDL;

- 2. Component declaration in the structural VHDL design;

- 3. Component instantiating.

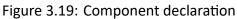

### Structural description example

On the following we will present the structural design style by designing a three bit shift register. The example starts from the the lowest level presenting a D type flip-flop design, followed by D type component declaration in the shift register VHDL program. Since the VHDL program is well commented the figures are self self-explanatory. First the rising edge controlled D flip-flop is presented (figure 3.21)

Figure 3.18: Structural system

```

1

2

3

:<instance name> : <component_name>

4

generic map (

5

<generic_name> => <value>,

6

<other generics>...

:)

7

8

port map (

9

<port_name> => <signal_name>,

10

<other ports>...

11 ;);

12

13 ¦

```

Figure 3.20: Component instantiating

then the hierarchical design of the shift register (figure 3.22) and finally the Schematic obtained from the VHDL code is presented.

Figure 3.21: D flip-flop VHDL example

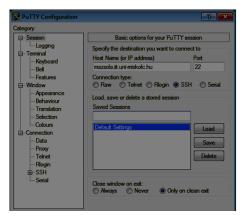

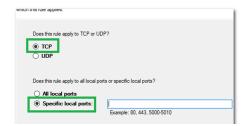

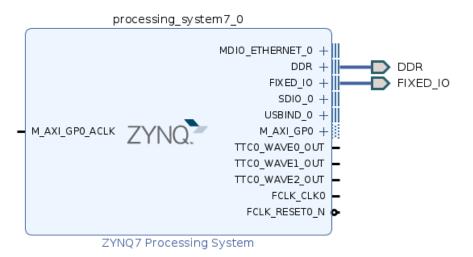

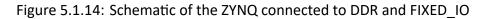

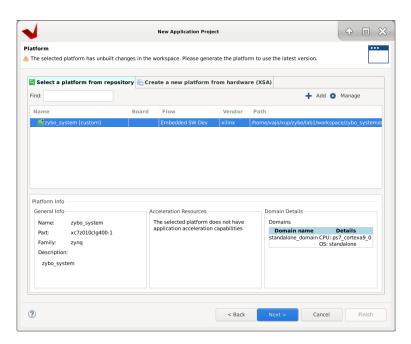

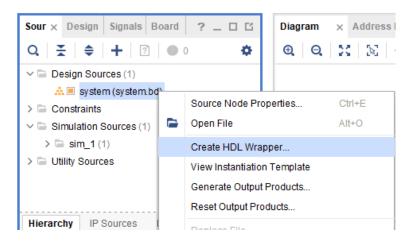

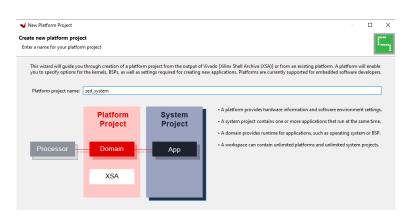

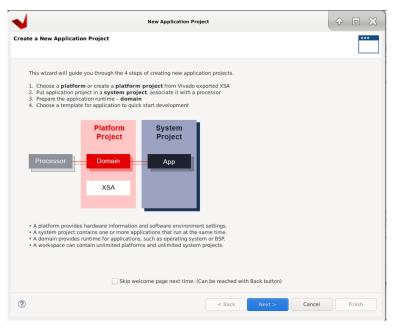

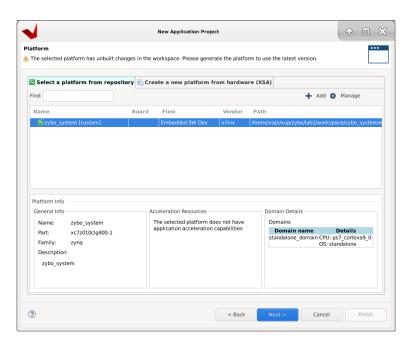

| <pre>23: use IEEE.STD_LOGIC_1164.ALL;<br/>240 entity shift_reg_ex is<br/>25: Port ( d_in : in STD_LOGIC; serial data input<br/>26: clk : in STD_LOGIC; clock rising edge is controlling the shift regiszter<br/>27: rst : in STD_LOGIC; reset when rst='1' then the outpust are q_out = '0'<br/>28: q_out : out STD_LOGIC_VECTOR (2 downto 0)); register output<br/>290 end shift_reg_ex;<br/>300 architecture Behavioral of shift_reg_ex is<br/>31: component declaration of D flip-flop<br/>220 component fdd<br/>33: port ( d : in STD_LOGIC; D flip-flop input<br/>34: rst : in STD_LOGIC; RESET when rst='1' then q='0'<br/>35: clk : in STD_LOGIC; CLK control clock<br/>36: q : out STD_LOGIC; O flip-flop outptu on rising edge clock<br/>370 end component;<br/>38: signal fqd : STD_LOGIC_VECTOR (2 downto 0);<br/>39 begin<br/>40: component instantiating bit 0, bit 1 ,bit2:<br/>410 fd0: fdd<br/>42: port map ( d =&gt; d_in,<br/>43: clk =&gt; clk,<br/>44: rst =&gt; rst,<br/>45: q =&gt; fqd(0) );<br/>46: fd1 : fdd<br/>47: port map ( d =&gt; fqd(0),<br/>48: clk =&gt; clk,<br/>49: rst =&gt; rst,</pre>                                                                |