# AN4660 Application note

# Migration of microcontroller applications from STM32F42xxx/F43xxx devices to STM32F7 Series devices

#### Introduction

The designers of STM32 microcontroller applications must have the possibility to easily replace one microcontroller type with another one from the same product family. The reasons for migrating an application to a different microcontroller can be for example:

- To fulfill higher product requirements, extra demands on the memory size, or an increased number of I/Os.

- To meet cost reduction constraints that require to switch to smaller components and to shrink the PCB area.

This application note analyzes the steps required to migrate from an existing STM32F42xxx/F43xxx device to a STM32F7 Series device based design.

This application note provides a guideline on the hardware migration and the peripheral migration. To fully benefit from this application note, the user should be familiar with the STM32 microcontroller family.

For additional information, refer to the following documents available on *www.st.com*:

- STM32F405/415, STM32F407/417, STM32F427/437 and STM32F429/439 advanced ARM<sup>®</sup>-based 32-bit MCUs reference manual (RM0090)

- STM32F72xxx and STM32F73xxx advanced ARM<sup>®</sup>-based 32-bit MCUs reference manual (RM0431)

- STM32F75xxx and STM32F74xxx advanced ARM<sup>®</sup>-based 32-bit MCUs reference manual (RM0385)

- STM32F76xxx and STM32F77xxx advanced ARM<sup>®</sup>-based 32-bit MCUs reference manual (RM0410)

| Туре              | Product lines and Series               |  |  |  |  |  |  |

|-------------------|----------------------------------------|--|--|--|--|--|--|

| Microcontrollers  | STM32F427/437 line, STM32F429/439 line |  |  |  |  |  |  |

| Wilcrocontrollers | STM32F7 Series                         |  |  |  |  |  |  |

#### Table 1. Applicable products

## Contents

| 1 | Hardware migration |                                                            |  |  |  |  |

|---|--------------------|------------------------------------------------------------|--|--|--|--|

|   | 1.1                | Pinout compatibility                                       |  |  |  |  |

|   |                    | 1.1.1 LQFP100 package6                                     |  |  |  |  |

|   |                    | 1.1.2 LQFP208 package                                      |  |  |  |  |

|   |                    | 1.1.3 LQFP176 package                                      |  |  |  |  |

|   |                    | 1.1.4         TFBGA216 package         12                  |  |  |  |  |

|   |                    | 1.1.5         LQFP64 package         14                    |  |  |  |  |

|   | 1.2                | Boot mode compatibility 15                                 |  |  |  |  |

|   | 1.3                | System bootloader                                          |  |  |  |  |

| 2 | Perip              | heral migration                                            |  |  |  |  |

|   | 2.1                | STM32 product cross-compatibility 17                       |  |  |  |  |

|   | 2.2                | Memory mapping                                             |  |  |  |  |

|   | 2.3                | Flash memory                                               |  |  |  |  |

|   | 2.4                | Embedded Flash memory 23                                   |  |  |  |  |

|   | 2.5                | Flexible memory controller (FMC) 24                        |  |  |  |  |

|   | 2.6                | Interrupt vectors                                          |  |  |  |  |

|   | 2.7                | External interrupt lines (EXTI) 26                         |  |  |  |  |

|   | 2.8                | RCC                                                        |  |  |  |  |

|   |                    | 2.8.1 Maximum frequency according to power scale parameter |  |  |  |  |

|   | 2.9                | PWR                                                        |  |  |  |  |

|   | 2.10               | RTC                                                        |  |  |  |  |

|   | 2.11               | U(S)ART                                                    |  |  |  |  |

|   | 2.12               | I2C                                                        |  |  |  |  |

|   | 2.13               | SPI                                                        |  |  |  |  |

|   | 2.14               | CRC                                                        |  |  |  |  |

|   | 2.15               | USB OTG                                                    |  |  |  |  |

|   | 2.16               | ADC                                                        |  |  |  |  |

|   |                    | 2.16.1 External trigger for regular channels               |  |  |  |  |

|   |                    | 2.16.2 External trigger for injected channels              |  |  |  |  |

| 3 | Conc               | lusion                                                     |  |  |  |  |

| 4 | <b>Revision history</b> |  | 38 |

|---|-------------------------|--|----|

|---|-------------------------|--|----|

## List of tables

| Table 1.  | Applicable products                                                                |

|-----------|------------------------------------------------------------------------------------|

| Table 2.  | STM32F42xxx/F43xxx and STM32F4xxx/F75xxx/F76xxx/F77xxx/F7x2xx                      |

|           | pinout differences (LQFP100)                                                       |

| Table 3.  | List of LQFP208 pinout differences                                                 |

| Table 4.  | List of LQFP176 pinout differences                                                 |

| Table 5.  | List of TFBGA216 ballout differences                                               |

| Table 6.  | Boot mode selection comparison between the STM32F42xxx/F43xxx and                  |

|           | STM32F7 Series devices                                                             |

| Table 7.  | STM32F42xxx/F43xxx and STM32F7 Series bootloader communication                     |

|           | peripherals                                                                        |

| Table 8.  | STM32 peripheral compatibility analysis between the STM32F42xxx/F43xxx and         |

|           | STM32F7 Series devices                                                             |

| Table 9.  | IP bus mapping differences between the STM32F42xxx/F43xxx and                      |

|           | STM32F7 Series devices                                                             |

| Table 10. | Flash memory differences between the STM32F42xxx/F43xxx                            |

|           | and STM32F7 Series devices                                                         |

| Table 11. | Flash module 1 Mbyte single bank organization (STM32F7 Series)                     |

| Table 12. | FMC differences between the STM32F42xxx/F43xxx and STM32F7 Series devices 24       |

| Table 13. | Interrupt vector differences between the STM32F42xxx/F43xxx and                    |

|           | STM32F7 Series devices                                                             |

| Table 14. | EXTI line differences between the STM32F42xxx/F43xxx and                           |

|           | STM32F7 Series devices                                                             |

| Table 15. | RCC differences between the STM32F42xxx/F43xxx and                                 |

|           | STM32F7 Series devices                                                             |

| Table 16. | Maximum frequency comparison between the STM32F42xxx/F43xxx and                    |

|           | STM32F7 Series devices                                                             |

| Table 17. | PWR differences between the STM32F42xxx/F43xxx and STM32F7 Series devices 29       |

| Table 18. | RTC comparison between the STM32F42xxx/F43xxx and STM32F7 Series devices 30        |

| Table 19. | U(S)ART differences between the STM32F42xxx/F43xxx and STM32F7 Series devices . 31 |

| Table 20. | I2C differences between the STM32F42xxx/F43xxx and STM32F7 Series devices 32       |

| Table 21. | SPI differences between the STM32F42xxx/F43xxx and STM32F7 Series devices 32       |

| Table 22. | CRC differences between the STM32F42xxx/F43xxx and STM32F7 Series devices 33       |

| Table 23. | USB OTG differences between the STM32F42xxx/F43xxx and                             |

|           | STM32F7 Series devices                                                             |

| Table 24. | External trigger for regular channel differences between the                       |

|           | STM32F42xxx/F43xxx and STM32F7 Series devices                                      |

| Table 25. | External trigger for injected channel differences between the                      |

|           | STM32F42xxx/F43xxx and STM32F7 Series devices                                      |

| Table 26. | Document revision history                                                          |

# List of figures

| Figure 1. | Incompatible board design for LQFP100 package | 6 |

|-----------|-----------------------------------------------|---|

| Figure 2. | LQFP208 pinout differences                    | 8 |

| Figure 3. | LQFP176 pinout differences                    | 0 |

| Figure 4. | TFBGA216 ballout differences 1                | 3 |

## **1** Hardware migration

#### 1.1 Pinout compatibility

#### 1.1.1 LQFP100 package

The STM32F74xxx/F75xxx/F76xxx/F77xxx/F7x2xx devices are fully pin-to-pin compatible with the STM32F42xxx/F43xxx devices except for the LQFP100 package, allowing the user to try different peripherals, and reaching higher performances (higher frequency) for a greater degree of freedom during the development cycle.

The STM32F7x3xx devices (x=2 or 3) are not compatible with the STM32F42xxx/F43xxx devices due to the USB PHY HS functionality on some pins.

In this application note, the pinout migration to the STM32F7x3xx product is not covered. In order to migrate to this product, refer to *Migration of microcontroller applications between* STM32F74xxx/75xxx and STM32F72xxx/F73xxx application note (AN4946).

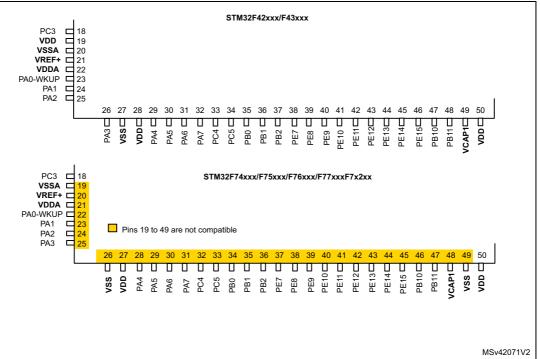

*Figure 1* and *Table 2* present the pinout differences between the STM32F42xxx/F43xxx and STM32F74xxx/F75xxx/F76xxx/F77xxx/F7x2xx devices for the LQFP100 package.

#### Figure 1. Incompatible board design for LQFP100 package

| LQFP100 | STM32F42xxx/F43xxx pinout | STM32F74xxx/F75xxx/<br>F76xxx/F77xxx/F76xxx/<br>F7x2xx pinout |  |  |  |  |

|---------|---------------------------|---------------------------------------------------------------|--|--|--|--|

| 19      | VDD                       | VSSA                                                          |  |  |  |  |

| 20      | VSSA                      | VREF+                                                         |  |  |  |  |

| 21      | VREF+                     | VDDA                                                          |  |  |  |  |

| 22      | VDDA                      | PA0-WKUP                                                      |  |  |  |  |

| 23      | PA0-WKUP                  | PA1                                                           |  |  |  |  |

| 24      | PA1                       | PA2                                                           |  |  |  |  |

| 25      | PA2                       | PA3                                                           |  |  |  |  |

| 26      | PA3                       | VSS                                                           |  |  |  |  |

| 27      | VSS                       | VDD                                                           |  |  |  |  |

| 28      | VDD                       | PA4                                                           |  |  |  |  |

| 29      | PA4                       | PA5                                                           |  |  |  |  |

| 30      | PA5                       | PA6                                                           |  |  |  |  |

| 31      | PA6                       | PA7                                                           |  |  |  |  |

| 32      | PA7                       | PC4                                                           |  |  |  |  |

| 33      | PC4                       | PC5                                                           |  |  |  |  |

| 34      | PC5                       | PB0                                                           |  |  |  |  |

| 35      | PB0                       | PB1                                                           |  |  |  |  |

| 36      | PB1                       | PB2                                                           |  |  |  |  |

| 37      | PB2                       | PE7                                                           |  |  |  |  |

| 38      | PE7                       | PE8                                                           |  |  |  |  |

| 39      | PE8                       | PE9                                                           |  |  |  |  |

| 40      | PE9                       | PE10                                                          |  |  |  |  |

| 41      | PE10                      | PE11                                                          |  |  |  |  |

| 42      | PE11                      | PE12                                                          |  |  |  |  |

| 43      | PE12                      | PE13                                                          |  |  |  |  |

| 44      | PE13                      | PE14                                                          |  |  |  |  |

| 45      | PE14                      | PE15                                                          |  |  |  |  |

| 46      | PE15                      | PB10                                                          |  |  |  |  |

| 47      | PB10                      | PB11                                                          |  |  |  |  |

| 48      | PB11                      | VCAP1                                                         |  |  |  |  |

| 49      | VCAP1                     | VSS                                                           |  |  |  |  |

| 53      | PB14                      | PB14                                                          |  |  |  |  |

| 54      | PB15                      | PB15                                                          |  |  |  |  |

# Table 2. STM32F42xxx/F43xxx and STM32F4xxx/F75xxx/F76xxx/F77xxx/F7x2xx pinout differences (LQFP100)

| LQFP100 | STM32F42xxx/F43xxx pinout | STM32F74xxx/F75xxx/<br>F76xxx/F77xxx/F76xxx/<br>F7x2xx pinout |

|---------|---------------------------|---------------------------------------------------------------|

| 55      | PD8                       | PD8                                                           |

| 56      | PD9                       | PD9                                                           |

| 57      | PD10                      | PD10                                                          |

# Table 2. STM32F42xxx/F43xxx and STM32F4xxx/F75xxx/F76xxx/F77xxx/F7x2xx pinout differences (LQFP100) (continued)

#### 1.1.2 LQFP208 package

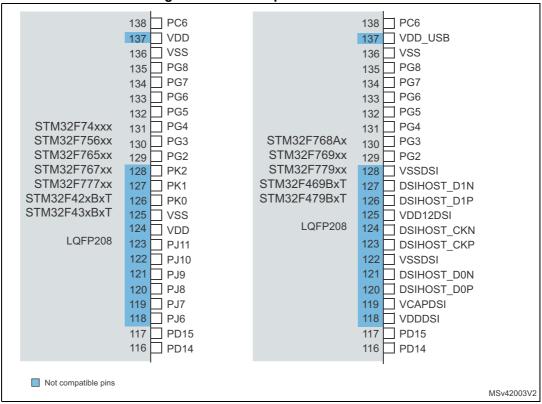

*Figure 2* and *Table 3* present the pinout differences between the STM32F74xxx/STM32F756xx/STM32F765xx/STM32F767xx/STM32F777xx/STM32F42xB xT/STM32F43xBxT and the

STM32F768Ax/STM32F769xx/STM32F779xx/STM32F469BxT/STM32F479BxT devices for the LQFP208 package.

Figure 2. LQFP208 pinout differences

For the highlighted (blue) terminals, the DSIHOST dedicated IOs on the STM32F768Ax/STM32F769xx/STM32F779xx/STM32F469BxT/STM32F479BxT devices substitute some of

STM32F74xxx/STM32F756xx/STM32F765xx/STM32F767xx/STM32F777xx/STM32F42xB xT/STM32F43xBxT IO ports.

| Terminal | STM32F74xxx<br>STM32F756xx<br>STM32F765xx<br>STM32F767xx<br>STM32F777xx<br>STM32F42xBxT<br>STM32F43xBxT | STM32F768Ax<br>STM32F769xx<br>STM32F779xx<br>STM32F469BxT<br>STM32F479BxT | Terminal | STM32F74xxx<br>STM32F756xx<br>STM32F765xx<br>STM32F767xx<br>STM32F777xx<br>STM32F42xBxT<br>STM32F43xBxT | STM32F768Ax<br>STM32F769xx<br>STM32F779xx<br>STM32F469BxT<br>STM32F479BxT |

|----------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 128      | PK2                                                                                                     | VSSDSI                                                                    | 122      | PJ10                                                                                                    | VSSDSI                                                                    |

| 127      | PK1                                                                                                     | DSIHOST_D1N                                                               | 121      | PJ9                                                                                                     | DSIHOST_D0N                                                               |

| 126      | PK0                                                                                                     | DSIHOST_D1P                                                               | 120      | PJ8                                                                                                     | DSIHOST_D0P                                                               |

| 125      | VSS                                                                                                     | VDD12DSI                                                                  | 119      | PJ7                                                                                                     | VCAPDSI                                                                   |

| 124      | VDD                                                                                                     | DSIHOST_CKN                                                               | 118      | PJ6                                                                                                     | VDDDSI                                                                    |

| 123      | PJ11                                                                                                    | DSIHOST_CKP                                                               | 137      | VDD                                                                                                     | VDD_USB                                                                   |

#### Table 3. List of LQFP208 pinout differences

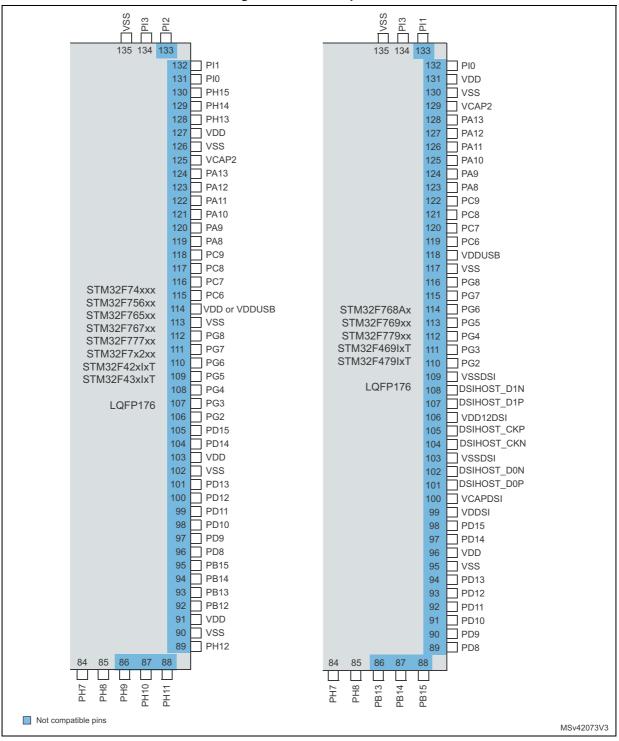

#### 1.1.3 LQFP176 package

*Figure 3* and *Table 4* present the pinout differences between the STM32F74xxx/STM32F756xx/STM32F765xx/STM32F767xx/STM32F777xx/STM32F7x2xx /STM32F42xlxT/STM32F43xlxT and the

STM32F768Ax/STM32F769xx/STM32F469IxT/STM32F479IxT devices for the LQFP176 package.

Figure 3. LQFP176 pinout differences

The highlighted (blue) terminals have different IO port assignment.

|          | Table 4. List of LQFP176 pinout differences                                                                            |                                                                           |  |  |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Terminal | STM32F74xxx<br>STM32F756xx<br>STM32F765xx<br>STM32F767xx<br>STM32F777xx<br>STM32F7x2xx<br>STM32F42xIxT<br>STM32F42xIxT | STM32F768Ax<br>STM32F769xx<br>STM32F779xx<br>STM32F469IxT<br>STM32F479IxT |  |  |  |  |  |  |  |

| 133      | PI2                                                                                                                    | PI1                                                                       |  |  |  |  |  |  |  |

| 132      | PI1                                                                                                                    | PIO                                                                       |  |  |  |  |  |  |  |

| 131      | PI0                                                                                                                    | VDD                                                                       |  |  |  |  |  |  |  |

| 130      | PH15                                                                                                                   | VSS                                                                       |  |  |  |  |  |  |  |

| 129      | PH14                                                                                                                   | VCAP2                                                                     |  |  |  |  |  |  |  |

| 128      | PH13                                                                                                                   | PA13                                                                      |  |  |  |  |  |  |  |

| 127      | VDD                                                                                                                    | PA12                                                                      |  |  |  |  |  |  |  |

| 126      | VSS                                                                                                                    | PA11                                                                      |  |  |  |  |  |  |  |

| 125      | VCAP2                                                                                                                  | PA10                                                                      |  |  |  |  |  |  |  |

| 124      | PA13                                                                                                                   | PA0                                                                       |  |  |  |  |  |  |  |

| 123      | PA12                                                                                                                   | PA8                                                                       |  |  |  |  |  |  |  |

| 122      | PA11                                                                                                                   | PC9                                                                       |  |  |  |  |  |  |  |

| 121      | PA10                                                                                                                   | PC8                                                                       |  |  |  |  |  |  |  |

| 120      | PA9                                                                                                                    | PC7                                                                       |  |  |  |  |  |  |  |

| 119      | PA8                                                                                                                    | PC6                                                                       |  |  |  |  |  |  |  |

| 118      | PC9                                                                                                                    | VDDUSB                                                                    |  |  |  |  |  |  |  |

| 117      | PC8                                                                                                                    | VSS                                                                       |  |  |  |  |  |  |  |

| 116      | PC7                                                                                                                    | PG8                                                                       |  |  |  |  |  |  |  |

| 115      | PC6                                                                                                                    | PG7                                                                       |  |  |  |  |  |  |  |

| 114      | VDD or VDDUSB                                                                                                          | PG6                                                                       |  |  |  |  |  |  |  |

| 113      | VSS                                                                                                                    | PG5                                                                       |  |  |  |  |  |  |  |

| 112      | PG8                                                                                                                    | PG4                                                                       |  |  |  |  |  |  |  |

| 111      | PG7                                                                                                                    | PG3                                                                       |  |  |  |  |  |  |  |

| 110      | PG6                                                                                                                    | PG2                                                                       |  |  |  |  |  |  |  |

| 109      | PG5                                                                                                                    | VSSDSI                                                                    |  |  |  |  |  |  |  |

| 108      | PG4                                                                                                                    | DSIHOST_D1N                                                               |  |  |  |  |  |  |  |

| 107      | PG3                                                                                                                    | DSIHOST_D1P                                                               |  |  |  |  |  |  |  |

| 106      | PG2                                                                                                                    | VDD12DSI                                                                  |  |  |  |  |  |  |  |

| 105      | PD15                                                                                                                   | DSIHOST_CKP                                                               |  |  |  |  |  |  |  |

| 104      | PD14                                                                                                                   | DSIHOST_CKN                                                               |  |  |  |  |  |  |  |

#### Table 4. List of LQFP176 pinout differences

| Terminal | STM32F74xxx<br>STM32F756xx<br>STM32F765xx<br>STM32F767xx<br>STM32F777xx<br>STM32F7x2xx<br>STM32F42xIxT<br>STM32F42xIxT | STM32F768Ax<br>STM32F769xx<br>STM32F779xx<br>STM32F469IxT<br>STM32F479IxT |

|----------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 103      | VDD                                                                                                                    | VSSDSI                                                                    |

| 102      | VSS                                                                                                                    | DSIHOST_D0N                                                               |

| 101      | PD13                                                                                                                   | DSIHOST_D0P                                                               |

| 100      | PD12                                                                                                                   | VCAPDSI                                                                   |

| 99       | PD11                                                                                                                   | VDDDSI                                                                    |

| 98       | PD10                                                                                                                   | PD15                                                                      |

| 97       | PD9                                                                                                                    | PD14                                                                      |

| 96       | PD8                                                                                                                    | VDD                                                                       |

| 95       | PB15                                                                                                                   | VSS                                                                       |

| 94       | PB14                                                                                                                   | PD13                                                                      |

| 93       | PB13                                                                                                                   | PD12                                                                      |

| 92       | PB12                                                                                                                   | PD11                                                                      |

| 91       | VDD                                                                                                                    | PD10                                                                      |

| 90       | VSS                                                                                                                    | PD9                                                                       |

| 89       | PH12                                                                                                                   | PD8                                                                       |

| 88       | PH11                                                                                                                   | PB15                                                                      |

| 87       | PH10                                                                                                                   | PB14                                                                      |

| 86       | PH9                                                                                                                    | PB13                                                                      |

#### Table 4. List of LQFP176 pinout differences (continued)

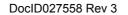

#### 1.1.4 TFBGA216 package

*Figure 4* and *Table 5* present the ballout differences between the STM32F74xxx/STM32F756xx/STM32F765xx/STM32F767xx/STM32F777xx/STM32F42xN xH/STM32F43xNxH and the STM32F768Ax/STM32F769xx/STM32F469NxH/STM32F479NxH devices for the TFBGA216 package.

|                | Figure 4. TFBGA216 ballout differences |                                 |                                                                      |                                        |       |      |      |      |                 |                                           |                         |                 |      |            |

|----------------|----------------------------------------|---------------------------------|----------------------------------------------------------------------|----------------------------------------|-------|------|------|------|-----------------|-------------------------------------------|-------------------------|-----------------|------|------------|

| 1              | 2                                      | 3                               | 4                                                                    | 5                                      | 6     | 7    | 8    | 9    | 10              | 11                                        | 12                      | 13              | 14   | 15         |

| A PE4          | PE3                                    | B PE2                           | PG14                                                                 | PE1                                    | PE0   | PB8  | PB5  | PB4  | PB3             | PD7                                       | PC12                    | PA15            | PA14 | PA13       |

| B PE           | 5 PEG                                  | 9 PG13                          | <b>PB9</b>                                                           | РВ7                                    | PB6   | PG15 | PG11 | PJ13 | PJ12            | PD6                                       | PD0                     | PC11            | PC10 | PA12       |

| С ИВА          | T PI8                                  | PI4                             | РК7                                                                  | PK6                                    | PK5   | PG12 | PG10 | PJ14 | PD5             | PD3                                       | PD1                     | PI3             | PI2  | PA11       |

| D PC1          | 3 PFC                                  | PI5                             | P17 (                                                                | PI10                                   | PI6   | PK4  | РКЗ  | PG9  | PJ15            | PD4                                       | PD2                     | PH15            | PI1  | PA10       |

| E PC1          | 4 PF1                                  | PI12                            | P19 (                                                                |                                        | зоото | VDD  | VDD  | VDD  | VDD             | VCAP2                                     | PH13                    | PH14            | PIO  | PA9        |

| F PC1          | 5 VSS                                  | B) PI11                         | VDD                                                                  | VDD                                    | vss   | VSS  | vss  | vss  | vss             | vss                                       |                         |                 | PC9  | PA8        |

| G PHO          | D PF2                                  | PI13                            | PI15                                                                 | VDD                                    | vss   |      |      |      | vss             |                                           | Ŏ                       |                 | PC8  | PC7        |

| Н РН           | I) (PF3                                | B PI14                          | PH4                                                                  |                                        | vss   |      |      |      | vss             | Ŏ                                         | Ŏ                       | Ŏ               | PG8  | PC6        |

| J NRS          | T PF4                                  | PH5                             | PH3                                                                  |                                        | vss   |      |      |      | vss             | VDD                                       | Ŏ                       | Ŏ               | PG7  | PG6        |

| K PF7          | PF6                                    | PF5                             | PH2                                                                  | VDD                                    | vss   | vss  | vss  | vss  | vss             | VDD                                       | Ŏ                       | PD15            | PB13 | PD10       |

| L PF1          | 0 PF9                                  | PF8                             |                                                                      | YPASS<br>-REG                          | vss   | VDD  | VDD  | VDD  | VDD             | VCAP1                                     | PD14                    | PB12            | PD9  | PD8        |

| M vss          | A PCC                                  | PC1                             | PC2                                                                  | PB2                                    | PF12  | PG1  | PF15 | PJ4  | PD12            | PD13                                      | PG3                     | PG2             | PJ5  | PH12       |

| N VRE          | F- PA1                                 | PA0                             | PA4                                                                  | PC4                                    | PF13  | PG0  | PJ3  | PE8  | PD11            | PG5                                       | PG4                     | PH7             | PH9  | PH11       |

| P VREF         | + PA2                                  | PA6                             | PA5                                                                  | PC5                                    | PF14  | PJ2  | PF11 | PE9  | PE11            | PE14                                      | PB10                    | PH6             | PH8  | PH10       |

| R VDD          | A PA3                                  | PA7                             | (PB1)                                                                | PB0                                    | PJ0   | PJ1  | PE7  | PE10 | PE12            | PE15                                      | PE13                    | PB11            | PB14 | PB15       |

|                |                                        | STI<br>STI<br>STI<br>STI<br>STM | M32F74<br>M32F75<br>M32F76<br>M32F76<br>M32F77<br>M32F42x<br>I32F42x | 6xx<br>5xx<br>7xx<br>7xx<br>7xx<br>NxH |       |      |      |      | ST<br>ST<br>STM | M32F7<br>M32F7<br>M32F7<br>J32F4<br>J32F4 | 769xx<br>779xx<br>69Nx⊦ |                 | TF   | BGA216     |

|                | F                                      | vss                             | PK1                                                                  | PL                                     | 2     |      | F    | V    | vss             | DSI<br>HOST<br>D1P                        | _ но                    | SI<br>ST_<br>1N |      |            |

|                | G                                      | VDD                             | PJ11                                                                 | РК                                     | 0     |      | G    |      | DDD<br>ISB      | VSS<br>DSI                                |                         | D12<br>SI       |      |            |

|                | н                                      | VDD                             | PJ8                                                                  | PJ1                                    | 10    |      | Н    |      |                 | DSI<br>HOST<br>CKP                        | _ но                    | SI<br>ST_<br>KN |      |            |

|                | J                                      | VDD                             | PJ7                                                                  | PJ                                     | 9     |      | J    | V    | 'DD             | DSI<br>HOST<br>DOP                        |                         | SI<br>ST_<br>ON |      |            |

|                | к                                      | VDD                             | PJ6                                                                  | PD                                     | 15    |      | к    | V    | DD              | VCAF                                      | PE                      | 015             |      |            |

| Not compatible | balls                                  | 11                              | 12                                                                   | 13                                     | 3     |      |      | 1    | 11              | 12                                        | 1                       | 3               |      | MSv42077V2 |

Figure 4. TFBGA216 ballout differences

For the highlighted (blue) terminals, the DSIHOST dedicated IOs on the STM32F768Ax/STM32F769xx/STM32F779xx/STM32F469NxH/STM32F479NxH devices substitute some of

STM32F74xxx/STM32F756xx/STM32F765xx/STM32F767xx/STM32F777xx/ STM32F42xNxH/STM32F43xNxH IO ports.

| Terminal | STM32F74xxx<br>STM32F756xx<br>STM32F765xx<br>STM32F767xx<br>STM32F777xx<br>STM32F42xNxH<br>STM32F43xNxH | STM32F768Ax<br>STM32F769xx<br>STM32F779xx<br>STM32F469NxH<br>STM32F479NxH | Terminal | STM32F74xxx<br>STM32F756xx<br>STM32F765xx<br>STM32F767xx<br>STM32F777xx<br>STM32F42xNxH<br>STM32F43xNxH | STM32F768Ax<br>STM32F769xx<br>STM32F779xx<br>STM32F469NxH<br>STM32F479NxH |

|----------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 11G      | VDD                                                                                                     | VDDDUSB                                                                   | 12K      | PJ6                                                                                                     | VCAPDSI                                                                   |

| 11H      | VDD                                                                                                     | VDDDSI                                                                    | 13F      | PL2                                                                                                     | DSIHOST_D1N                                                               |

| 12F      | PK1                                                                                                     | DSIHOST_D1P                                                               | 13G      | PK0                                                                                                     | VDD12DSI                                                                  |

| 12G      | PJ11                                                                                                    | VSSDSI                                                                    | 13H      | PJ10                                                                                                    | DSIHOST_CKN                                                               |

| 12H      | PJ8                                                                                                     | DSIHOST_CKP                                                               | 13J      | PJ9                                                                                                     | DSIHOST_D0N                                                               |

| 12J      | PJ7                                                                                                     | DSIHOST_D0P                                                               | -        | -                                                                                                       | -                                                                         |

#### 1.1.5 LQFP64 package

The LQFP64 is available on the STM32F7x2xx devices.

#### 1.2 Boot mode compatibility

The STM32F42xxx/F43xxx boot space is based on boot mode selection pins: BOOT0 and BOOT1 while the STM32F7 Series boot space is based on BOOT0 and boot address option bytes as described in *Table 6*.

For the STM32F74xxx/F75xxx devices, the boot base address supports any address in the range from 0x0000 0000 to 0x2004 FFFF while the STM32F76xxx/F77xxx devices extend the boot address to any address in the range from 0x0000 0000 to 0x2007 FFFF. The STM32F7x2xx/F7x3xx devices allow to program any boot memory address from 0x0000 0000 to 0x3FFF FFFF.

| Table 6. Boot mode selection comparison between the STM32F42xxx/F43xxx and |

|----------------------------------------------------------------------------|

| STM32F7 Series devices                                                     |

| STM32F7 Series   |                 |                                                                                                                     |                                                                                                                 |  |  |  |

|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| Во               | ot mode s       | selection                                                                                                           |                                                                                                                 |  |  |  |

| во               | ОТ              | Boot address<br>Option Bytes                                                                                        | Boot space                                                                                                      |  |  |  |

| (                | )               | BOOT_ADD0<br>[15:0]                                                                                                 | Boot address defined by user option byte BOOT_ADD0[15:0]<br>- ST programmed value: Flash on ITCM at 0x0020 0000 |  |  |  |

| 1                | 1               | BOOT_ADD1Boot address defined by user option byte BOOT_ADD1[15:0]- ST programmed value: system bootloader at 0x0010 |                                                                                                                 |  |  |  |

|                  |                 |                                                                                                                     | STM32F42xxx/F43xxx                                                                                              |  |  |  |

| Boot<br>selectio | mode<br>on Pins | Boot Mode                                                                                                           | Aliasing                                                                                                        |  |  |  |

| BOOT1            | BOOT0           |                                                                                                                     |                                                                                                                 |  |  |  |

| x                | 0               | Main Flash<br>memory                                                                                                | Main Flash memory is selected as the boot space at 0x0800 0000                                                  |  |  |  |

| 0                | 1               | System<br>memory                                                                                                    | System memory is selected as the boot space at 0x1FFF 0000                                                      |  |  |  |

#### 1.3 System bootloader

The system bootloader is located in the system memory, programmed by ST during the production. It is used to reprogram the Flash memory using one of the following serial interfaces.

Table 7 shows the supported communication peripherals by the system bootloader.

| Table 7. STM32F42xxx/F43xxx and STM32F7 Series bootloader communication |

|-------------------------------------------------------------------------|

| peripherals                                                             |

| System bootloader<br>peripherals   | STM32F42xxx/F43xxx I/O pin  | STM32F7 Series I/O pin    |  |  |

|------------------------------------|-----------------------------|---------------------------|--|--|

| DFU                                | USB OTG FS (PA11 /          | PA12) in device mode      |  |  |

| USART1                             | PA9 /                       | PA10                      |  |  |

| USART3                             | PB10 / PB11 and PC10 / PC11 |                           |  |  |

| CAN2<br>CAN1 in STM32F72xxx/F73xxx | PB5 / PB13<br>C PB8/PB9     |                           |  |  |

| I2C1                               | NA                          | PB6 / PB9                 |  |  |

| I2C2                               | NA                          | PF0 / PF1                 |  |  |

| I2C3                               | NA                          | PA8 / PC9                 |  |  |

| SPI1                               | NA                          | PA4 / PA5 / PA6 / PA7     |  |  |

| SPI2                               | NA                          | PI0 / PI1 /PI2/ PI3       |  |  |

| SPI4                               | NA                          | PE11 / PE12 / PE13 / PE14 |  |  |

By default, in the STM32F7 Series devices, when the boot from system bootloader is selected, the code is executed from the ITCM interface. It could be reprogrammed by option byte executed from the AXIM interface. For more details on system bootloader refer to AN2606.

## 2 Peripheral migration

#### 2.1 STM32 product cross-compatibility

The STM32 series embed a set of peripherals which can be classed in three categories:

- The first category is for the peripherals which are by definition common to all products. Those peripherals are identical, so they have the same structure, registers and control bits. There is no need to perform any firmware change to keep the same functionality at the application level after migration. All the features and behavior remain the same.

- The second category is for the peripherals which are shared by all STM32 products but have only minor differences (in general to support new features), so the migration from one product to another is very easy and does not need any significant new development effort.

- The third category is for peripherals which have been considerably changed from one product to another (new architecture, new features...). For this category of peripherals, the migration will require a new development at application level.

- The SW compatibility mentioned in the *Table 8* only refers to the register description for "low level" drivers.

The Cube Hardware Abstraction Layer (HAL) is compatible between the STM32F42xxx/F43xxx and STM32F7 Series devices.

*Table 8* shows the STM32 peripheral compatibility between the STM32F42xxx/F43xxx and STM32F7 Series devices.

| Peripherals              |                  | STM32F42xxx<br>/F43xxx    | STM32F74xxx<br>/F75xxx | STM32F76xxx<br>/F77xxx | STM32F72xxx<br>/F73xxx | (   | Compatibility |

|--------------------------|------------------|---------------------------|------------------------|------------------------|------------------------|-----|---------------|

| -                        |                  | -                         |                        | -                      | -                      | SW  | Comments      |

| Flash memory in<br>Kbyte |                  | 2048                      | 1024                   | 2048                   | 512                    |     |               |

| SRAM                     | System           | 256<br>(115+16+64+<br>64) | 320<br>(240+16+64)     | 512<br>(386+16+128)    | 256<br>(176+16+64)     | -   | -             |

| (Kbyte)                  | Instruction      | NA                        | 16                     | 16                     | 16                     |     |               |

|                          | Backup           | 4                         | 4                      | 4                      | 4                      |     |               |

|                          | GP               | 10                        | 10                     | 10                     | 10                     | Yes | -             |

| Timers                   | Advanced control | 2                         | 2                      | 2                      | 2                      | Yes | -             |

|                          | Basic            | 2                         | 2                      | 2                      | 2                      | Yes | -             |

|                          | Low-power        | NA                        |                        | 1                      | 1                      | NA  | -             |

# Table 8. STM32 peripheral compatibility analysis between the STM32F42xxx/F43xxx and STM32F7 Series devices

| Peripherals              |                      | STM32F42xxx<br>/F43xxx  | STM32F74xxx<br>/F75xxx | STM32F76xxx<br>/F77xxx                           | STM32F72xxx<br>/F73xxx | (          | Compatibility                                                                                   |  |

|--------------------------|----------------------|-------------------------|------------------------|--------------------------------------------------|------------------------|------------|-------------------------------------------------------------------------------------------------|--|

|                          | Quad-SPI             | No                      |                        | Yes                                              |                        |            | -                                                                                               |  |

|                          | SPI / I2S            | 6/2 (full<br>duplex)    |                        | 4/3 (simplex)<br>6/3 (simplex) <sup>(1)</sup> 5/ |                        | No/<br>Yes | I2S compatible.                                                                                 |  |

|                          | I2C                  | 3                       | 2                      | 1                                                | 3                      | No         | Programmable<br>clock source for<br>STM32F7 Series                                              |  |

|                          | USART/<br>UART       | 4/4                     | 4/                     | /4                                               | 4/4                    | No         | Additional features<br>on STM32F7<br>Series                                                     |  |

| on interfaces            | USB OTG<br>FS        | Yes                     | Ye                     | 25                                               | Yes                    | No         | Dedicated<br>VDDUSB<br>More endpoints on<br>STM32F7 Series                                      |  |

| Communication interfaces | USB OTG<br>HS        | Yes                     | Ye                     | Yes                                              |                        | No         | More endpoints<br>and host channels<br>with an embedded<br>HS PHY in the<br>STM32F7x3 line      |  |

|                          | CAN                  | 2                       | 2 3                    |                                                  | 1                      | Yes        | -                                                                                               |  |

|                          | SAI                  | 1                       |                        | 2                                                |                        | Yes        | -                                                                                               |  |

|                          | SDIO/<br>SDMMC1      | Yes                     | Yes                    | 2x                                               | 2x                     | Yes        | New clock source<br>for SDMMC1 on<br>STM32F7 Series<br>with dedicated<br>supply for SDM-<br>MC2 |  |

|                          | SPDIFRX              | No                      | 4 inputs               |                                                  | NA                     | NA         | -                                                                                               |  |

|                          | RNG                  | Yes                     | Yes                    |                                                  | Yes                    | Yes        | -                                                                                               |  |

|                          | emory con-<br>roller | Yes                     | Yes                    |                                                  | Yes                    | Yes        | -                                                                                               |  |

| Et                       | hernet               | Yes                     | Ye                     | es                                               | NA                     | Yes        | -                                                                                               |  |

| N                        | IDIOS                | No                      | No                     | Yes                                              | NA                     | NA         | -                                                                                               |  |

| HD                       | MI-CEC               | No                      | Ye                     | es                                               | NA                     | NA         | -                                                                                               |  |

| [                        | DCMI                 | Yes                     | Ye                     | es                                               | NA                     | Yes        | -                                                                                               |  |

| WWDG                     |                      | WWDG Yes                |                        | es                                               | Yes                    | Yes        | -                                                                                               |  |

| ľ                        | WDG                  | Yes                     | Ye                     | es                                               | Yes                    | Yes        | -                                                                                               |  |

|                          | CRC                  | Yes                     | Ye                     | 28                                               | Yes                    | Yes        | Additional features<br>on STM32F7<br>Series                                                     |  |

| LC                       | D-TFT                | No   Yes <sup>(3)</sup> | Ye                     | es                                               | NA                     | Yes        | -                                                                                               |  |

# Table 8. STM32 peripheral compatibility analysis between the STM32F42xxx/F43xxx andSTM32F7 Series devices (continued)

# Table 8. STM32 peripheral compatibility analysis between the STM32F42xxx/F43xxx and STM32F7 Series devices (continued)

| 51M32F7 Series devices (continued) |                    |                        |                        |                        |                                                |               |                                                                       |     |                      |     |  |     |                                             |

|------------------------------------|--------------------|------------------------|------------------------|------------------------|------------------------------------------------|---------------|-----------------------------------------------------------------------|-----|----------------------|-----|--|-----|---------------------------------------------|

| Peripherals STM32F42xxx<br>/F43xxx |                    | STM32F42xxx<br>/F43xxx | STM32F74xxx<br>/F75xxx | STM32F76xxx<br>/F77xxx | STM32F72xxx<br>/F73xxx                         | Compatibility |                                                                       |     |                      |     |  |     |                                             |

| DS                                 | I-HOST             | No                     | No                     | Yes                    | NA                                             | NA            | New feature on<br>STM32F7x9xx/<br>Fx8xx                               |     |                      |     |  |     |                                             |

| J                                  | IPEG               | No                     | No                     | Yes                    | NA                                             | NA            | New feature on<br>STM32F76xxx/<br>F77xxx                              |     |                      |     |  |     |                                             |

| I                                  | DMA                |                        | DMA1-DMA2 (            | 8 stream each)         |                                                | Yes           | -                                                                     |     |                      |     |  |     |                                             |

|                                    | 1-ART-Acc<br>MA2D) | Yes                    | Ye                     | es                     | NA                                             | Yes           | -                                                                     |     |                      |     |  |     |                                             |

| C                                  | rypto              | Yes                    | Ye                     | es                     | Yes (AES256)                                   | Yes           | -                                                                     |     |                      |     |  |     |                                             |

| I                                  | lash               | Yes                    | Ye                     | es                     | NA                                             | Yes           | -                                                                     |     |                      |     |  |     |                                             |

| (                                  | GPIO               | Up to 168              | Up to 168              |                        | 140 in<br>STM32F7x2xx<br>138 in<br>STM32F7x3xx | Yes           | -                                                                     |     |                      |     |  |     |                                             |

| DF                                 | SDM1               | No                     | No                     | 4 filters              | NA                                             | NA            | New feature on<br>STM32F76xxx/<br>F77xxx                              |     |                      |     |  |     |                                             |

|                                    | 12 bits            | 3                      | 3                      |                        | 3                                              |               |                                                                       |     |                      |     |  |     |                                             |

| ADC                                | Number of channels | 16 24                  | 16                     | 24                     | 16 24                                          | Yes           | ADC Timer Trigger<br>not compatible                                   |     |                      |     |  |     |                                             |

|                                    | 12 bits            | Yes                    | Ye                     | es                     | Yes                                            |               |                                                                       |     |                      |     |  |     |                                             |

| DAC                                | Number of channels | 2                      | :                      | 2                      | 2                                              | Yes           | -                                                                     |     |                      |     |  |     |                                             |

| I                                  | EXTI               | Yes                    | Yes                    |                        | Yes                                            | Yes           | New EXTI line for<br>LPTIM1                                           |     |                      |     |  |     |                                             |

|                                    | RCC                | Yes                    | Yes                    |                        | Yes Yes                                        |               | Yes                                                                   | Yes | New LSE drive modes. |     |  |     |                                             |

| RTC                                |                    | Yes Yes                |                        | Yes                    |                                                | Yes           |                                                                       | Yes |                      | Yes |  | Yes | Additional features<br>on STM32F7<br>Series |

| F                                  | PWR                | Yes                    | Y                      | es                     | Yes                                            | Yes           | New wakeup pins<br>with configurable<br>polarity on<br>STM32F7 Series |     |                      |     |  |     |                                             |

| SY                                 | ′SCFG              | Yes                    | Ye                     | es                     | Yes                                            | Yes           | -                                                                     |     |                      |     |  |     |                                             |

1. SPI / I2S: 4/3 for 100 pin package and 6/3 for other packages.

2. SPI / I2S: 3/3 for 64 pin package, 4/3 for 100 pin package and 5/3 for other packages.

3. LCD - TFT:

- No: not available for the STM32F437xx devices.

- Yes: available for the STM32F439xx devices.

#### 2.2 Memory mapping

*Table 9* presents the peripheral address mapping differences between the STM32F42xxx/F43xx and STM32F7 Series devices.

# Table 9. IP bus mapping differences between the STM32F42xxx/F43xxx and STM32F7 Series devices

|                              | STMSZF7 Series devices |                              |                                 |                              |                                             |  |  |  |  |

|------------------------------|------------------------|------------------------------|---------------------------------|------------------------------|---------------------------------------------|--|--|--|--|

| Peripheral                   | Bus                    | STM32F42xxx<br>/F43xxx       | STM32F74xxx<br>/F75xxx          | STM32F76xxx<br>/F77xxx       | STM32F72xxx<br>/F73xxx                      |  |  |  |  |

|                              |                        | Base address                 | Base                            | address                      | Base address                                |  |  |  |  |

| Quad-SPI control register    | AHB3                   | NA                           | 0xA000 1000 - 0xA0001FFF        |                              |                                             |  |  |  |  |

| SAI2                         | APB2                   | NA                           | 0x4                             | 001 5C00 - 0x4001 5          | SFFF                                        |  |  |  |  |

| HDMI-CEC                     |                        | NA                           | 0x4000 6C00                     | - 0x4000 6FFF                | NA                                          |  |  |  |  |

| I2C4                         |                        | NA                           | 0x4000 6000                     | - 0x4000 63FF                | NA                                          |  |  |  |  |

| I2S3ext                      | APB1                   | 0x4000 4000 -<br>0x4000 43FF |                                 | NA                           |                                             |  |  |  |  |

| SPDIFRX                      | AFDI                   | NA                           | 0x4000 4000 - 0x4000 43FF<br>NA |                              | NA                                          |  |  |  |  |

| I2S2ext                      |                        | 0x4000 3400 -<br>0x4000 37FF |                                 |                              |                                             |  |  |  |  |

| LPTIM1                       |                        | NA                           | 0x4                             | 7FF                          |                                             |  |  |  |  |

| USB OTG PHY HS<br>controller | APB2                   | NA                           | NA                              | NA                           | 0x4001 7C00 -<br>0x4001 7FFF <sup>(1)</sup> |  |  |  |  |

| SDMMC2                       | APB2                   | NA                           | NA                              | 0x4001 1C00 -                | 0x4001 1FFF                                 |  |  |  |  |

| DSI-HOST                     | APB2                   | NA                           | NA                              | 0x4001 6C00 -<br>0x4001 73FF | NA                                          |  |  |  |  |

| JPEG                         | AHB2                   | NA                           | NA                              | 0x5005 1000 -<br>0x5005 1FFF | NA                                          |  |  |  |  |

| CAN3                         | APB1                   | NA                           | NA 0x4000 3400 -<br>0x4000 37FF |                              | NA                                          |  |  |  |  |

| DFSDM1                       | APB2                   | NA                           | NA                              | 0x4001 7400 -<br>0x4001 77FF | NA                                          |  |  |  |  |

| MDIOS                        | APB2                   | NA                           | NA                              | 0x4001 7800 -<br>0x4001 7BFF | NA                                          |  |  |  |  |

1. Only for the STM32F7x3xx devices.

### 2.3 Flash memory

*Table 10* presents the differences between the Flash memory interface of the STM32F42xxx/F43xxx and STM32F7 Series devices.

The STM32F74xxx/F75xxx devices instantiate a different Flash module both in terms of architecture and interface. For more information on the programming, erasing and protection of the STM32F74xxx/F75xxx Flash memory, refer to the STM32F74xxx and STM32F75xxx reference manual (RM0385).

DocID027558 Rev 3

For more information on programming, erasing and protection of the STM32F76xxx/F77xxx Flash memory, refer to the STM32F76xxx and STM32F77xxx reference manual (RM0410).

For more information on programming, erasing and protection of the STM32F72xxx/F73xxx Flash memory, refer to the STM32F72xxx and STM32F73xxx reference manual (RM0431).

| Flash                               | STM32F42xxx<br>/F43xxx                                                                                                                                           | STM32F74xxx<br>/F75xxx                                                                                                                                                  | STM32F76xxx<br>/F77xxx                                                                                                                                                                                                                                                                                                                                                                    | STM32F72xxx<br>/F73xxx                                                                                                                                                    |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | 0x0800 0000 – 0x081F<br>FFFF                                                                                                                                     | 0x0800 0000 - 0x080F<br>FFFF<br>(on AXIM interface)                                                                                                                     | 0x0800 0000 - 0x080F<br>FFFF<br>(on AXIM interface)                                                                                                                                                                                                                                                                                                                                       | 0x0800 0000 -<br>0x0807 FFFF                                                                                                                                              |

| Main/program<br>memory              | <ul> <li>Up to 2 Mbytes</li> <li>Split in 2 banks</li> <li>4 sectors of 16 Kbytes</li> <li>1 sector of 64 Kbytes</li> <li>6 sectors of<br/>128 Kbytes</li> </ul> | <ul> <li>Up to 1 Mbyte</li> <li>Split in 1 bank</li> <li>4 sectors of<br/>32 Kbytes</li> <li>1 sector of<br/>128 Kbytes</li> <li>3 sectors of<br/>256 Kbytes</li> </ul> | <ul> <li>Up to 2 Mbytes</li> <li>configurable in 1 (or<br/>2) bank (s)</li> <li>In single bank:</li> <li>4 sectors of 32<br/>Kbytes</li> <li>1 sector of 128<br/>Kbytes</li> <li>7 sectors of 256<br/>Kbytes</li> <li>In dual bank:</li> <li>Each bank is composed of:</li> <li>4 sectors of 16<br/>Kbytes</li> <li>1 sector of 64 Kbytes</li> <li>7 sectors of 128<br/>Kbytes</li> </ul> | <ul> <li>Up to 512 Kbytes</li> <li>Split in 1 bank</li> <li>4 sectors of 16<br/>Kbytes</li> <li>1 sector of 64<br/>Kbytes</li> <li>3 sectors of 128<br/>Kbytes</li> </ul> |

| Features                            | <ul> <li>– 128 bit wide data read</li> <li>– Read while Write<br/>(RWW)</li> </ul>                                                                               | – 256 bit wide data<br>read                                                                                                                                             | <ul> <li>256 bit wide data<br/>read in single Bank<br/>mode</li> <li>128 bit wide data<br/>read in dual Bank<br/>mode</li> </ul>                                                                                                                                                                                                                                                          | <ul> <li>– 128 bit wide data<br/>read</li> </ul>                                                                                                                          |